オリジナルの無線LANをFPGAで作ろう 8ページ目

過去の記事はこちら 1ページ目 2ページ目 3ページ目

4ページ目 5ページ目 6ページ目 7ページ目

1-送信側の回路図

FPGAに周辺部品を取り付けて送信側全体の回路を作ります。

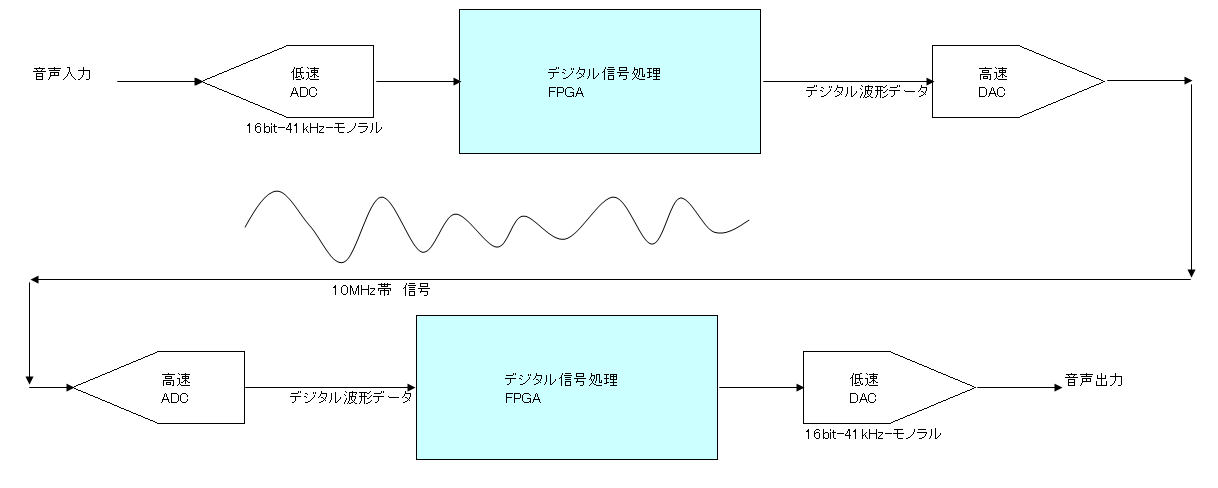

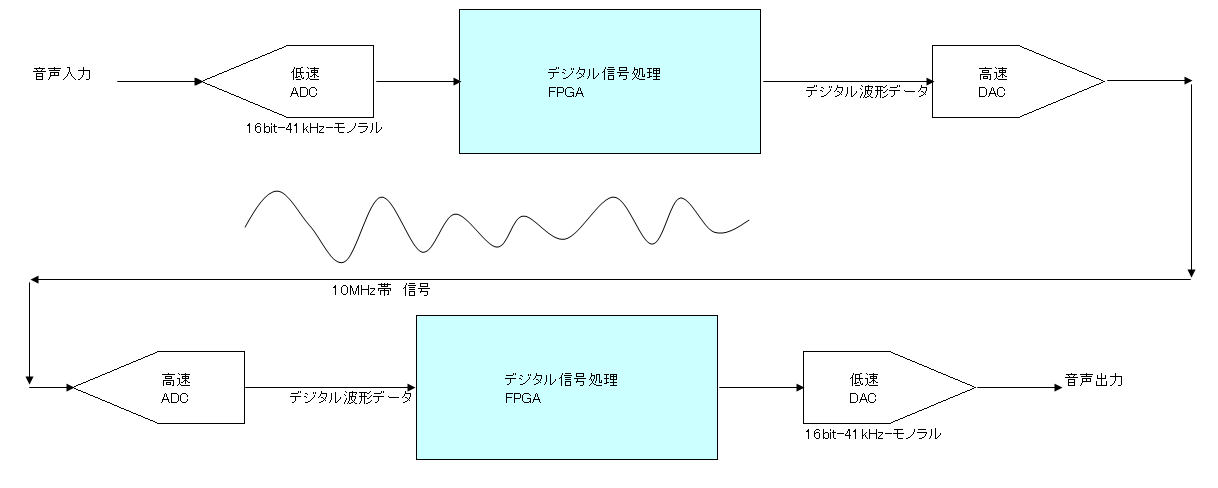

1ページ目に載せた送信+受信のブロック図を再掲いたします。

送信側はFPGAと低速ADCと高速DACで構成されます。

ブロック図を元に回路図を描いてみました。回路図のPDFをこちらからダウンロードしてください。

回路図は1ページに収まりませんでしたので、FPGAまわりはページを分けました。

低速ADCには入力アンプを、高速DACには出力バッファアンプをつけています。

高速ADCにはAD9744を採用しました。AD9744のデータシートは

こちらからダウンロードできます。

FPGAやADCやDACやアンプ類以外にも、電源供給部をもっています。

電源はDC5Vで、ACアダプタから供給するようにしました。

次回はFPGAに回路図に沿ったピンアサインを入力してコンパイルを確認します。

FPGAにピンアサインを入れてコンパイル確認の結果により回路図を変更する場合があります。

基板設計の際に、信号線の引き回しの都合で回路図を変更する場合もあります。

2015年1月23日 記

9ページ目に続く

戻る