�I���W�i���̖���LAN��FPGA�ō�낤 7�y�[�W��

�ߋ��̋L���͂����� 1�y�[�W�� 2�y�[�W�� 3�y�[�W��

4�y�[�W���@5�y�[�W���@6�y�[�W��

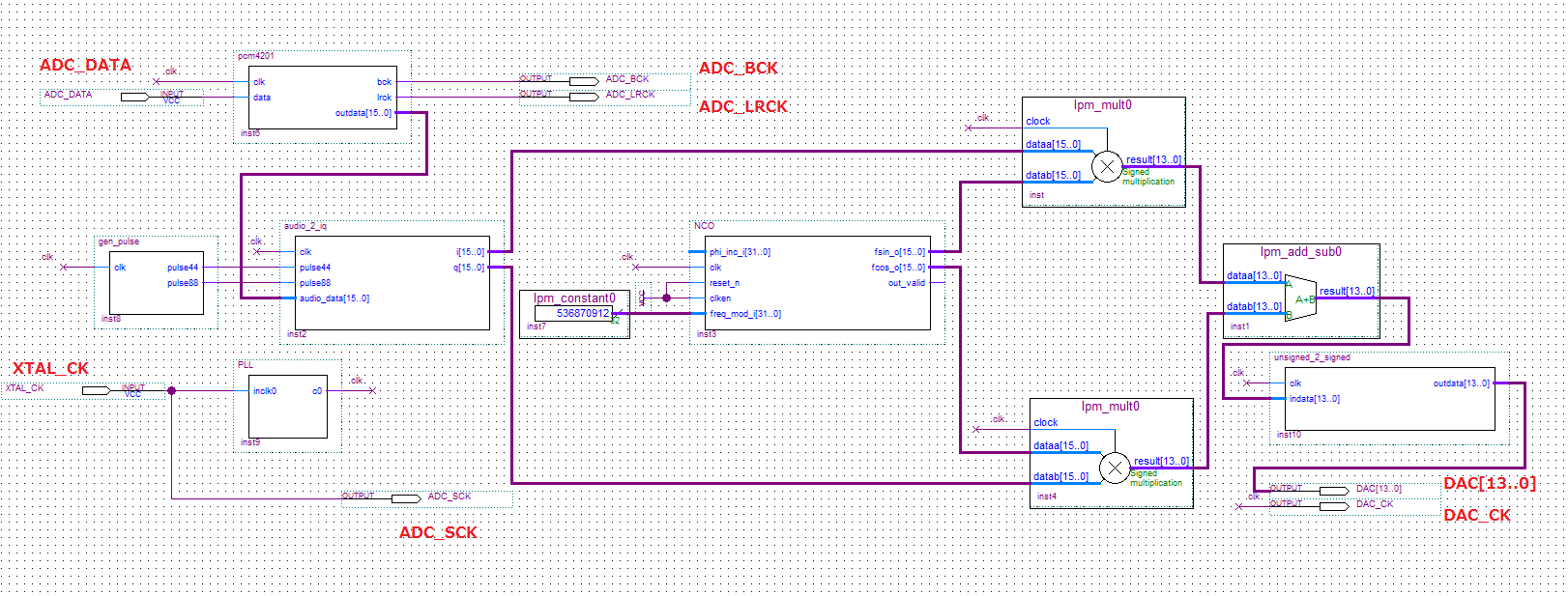

1-���MFPGA-2�̕␔�ϊ���H

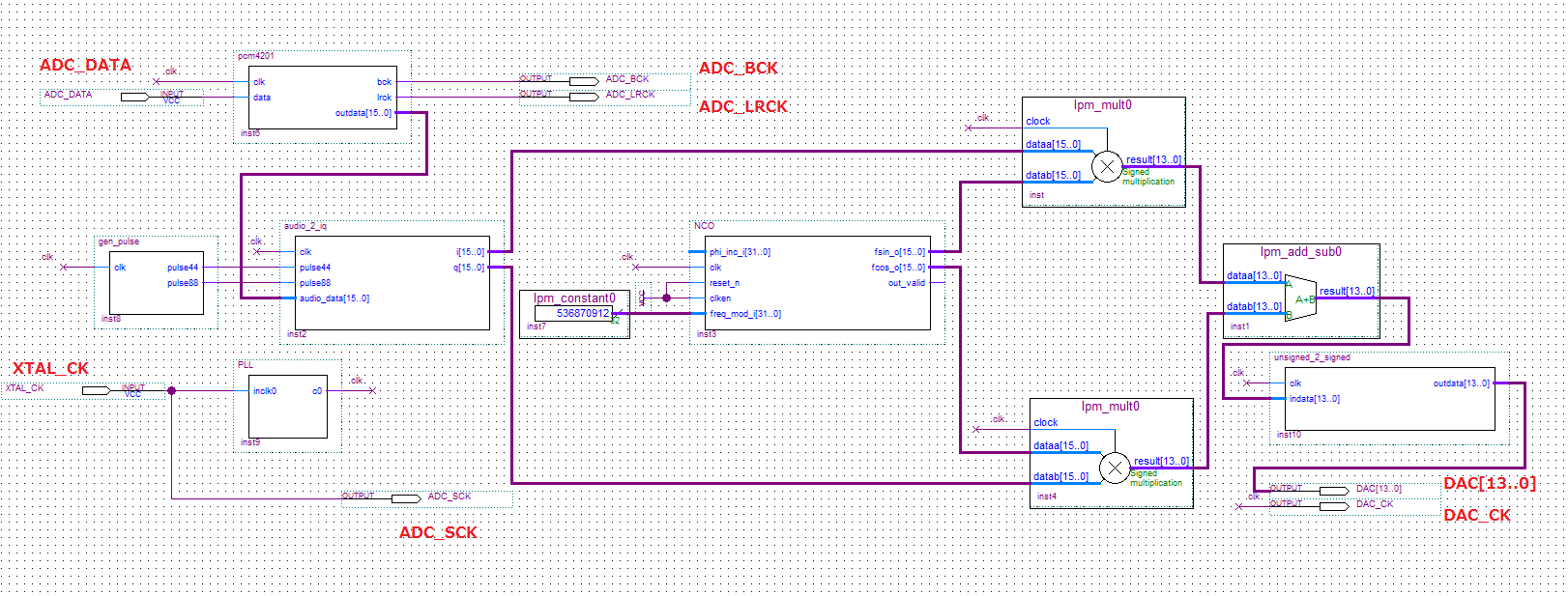

6�y�[�W�ڂ���̂Â��ł��BFPGA�̃t�@�[���E�F�A������Ă����܂��B

����܂ō���Ă���IQ�ϒ����10MHz�̔g�`�f�[�^��14�r�b�g2�̕␔�ŏo�͂��܂��B

����A�g�p����DAC��14�r�b�g�I�t�Z�b�g�o�C�i���ł��̂ŁA�f�[�^�`����ϊ����郂�W���[�����K�v�ɂȂ�܂��B

���W���[���̖��O��unsigned_2_signed�ɂ��܂��Bunsigned_2_signed���W���[����Verilog�ō��܂��B

unsigned_2_signed���W���[���̃\�[�X�R�[�h������������_�E�����[�h���Ă��������B

�R�[�h���_�E�����[�h���܂�����audio_2_iq�Ɠ����悤�ɂ��ăR�[�h����H�}�ɑg�ݍ��݂܂��B

��H�}�ɑg�ݍ��ގ菇�̏ڍׂ́A5�y�[�W����������������

2-���MFPGA-IO�s���̔z�u

�ȏ�ő��M�ɕK�v�ȃ��W���[�����쐬���I���܂����B�Ō��FPGA��IO�s�������܂��B

IO�s����lj����邽�߂ɉ�H�}�����_�u���N���b�N���ăV���{���ꗗ���o���܂��B�V���{���ꗗ����libraries��primitives��pin�@������͂������͏o�̓s���I�т܂��B

FPGA�̓��o�̓s�������Ċ���������Ԃ����}�ł��B

FPGA�̃s���ɖ��O�̓f�t�H���g�̂܂܂ɂȂ��Ă��܂�����A�s������ҏW���܂��B�s�������������Č��ɂ����ł��̂ŁA�Ԃ̑傫�ȕ����ŏ����܂����B

�s�����̂���������_�u���N���b�N����ƃs������ҏW�ł��܂��B

�O�܂ł̃y�[�W�ō쐬�������W���[���Ɉꕔ�ԈႢ������܂��̂ł����ŏC�����܂��B

10MHz�̔��UNCO��18�r�b�g�o�͂ɂȂ��Ă��܂��̂�16�r�b�g�ɏC�����܂��B

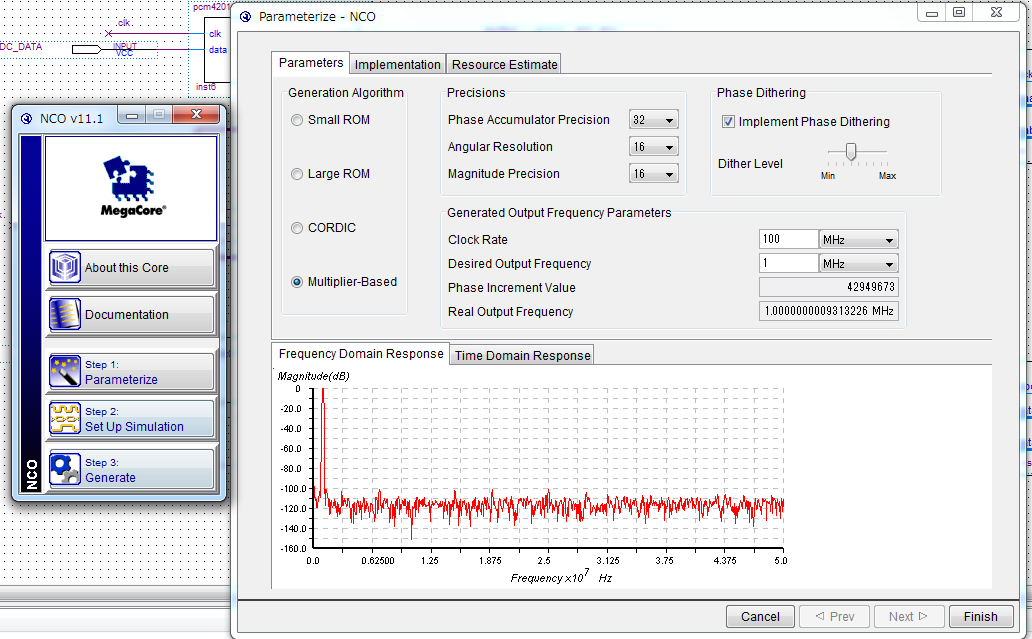

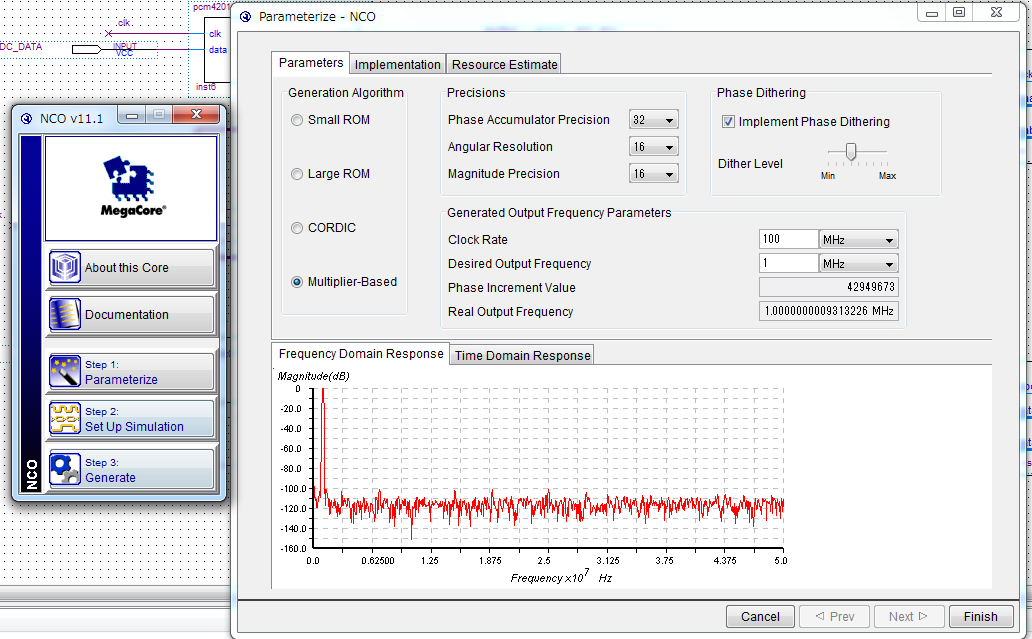

NCO���_�u���N���b�N����ƁANCO��������Ƃ��̃E�B�U�[�h���\������܂��B

�E�B�U�[�h��Step1 parameterize���N���b�N����parameterize�_�C�A���O���J���܂��Bparameterize�_�C�A���O��parameters�^�u�̒��ɂ���Magnitude Pricision��16�r�b�g�ɕύX���܂��B

parameterize�_�C�A���O��Finish���N���b�N���āA�E�B�U�[�h��Step3 generate���N���b�N����NCO�̏C���͊����ł��B

�����܂Ŋ�������ƃR���p�C�����ʂ�܂��B���C�����j���[�@���@processing ���@Start Compilation�ŃR���p�C�����ʂ邩�m�F���܂��B

C����ȂǂƈႢFPGA�̓V���v���ȍ\���ł��R���p�C���ɑ����̎��Ԃ�������܂��B����PC�iCore-i3 2120T 2.6GHz�j�ł�51�b������܂����B

�v���O���~���O����ł̃R���p�C����"printf"�Ȃǂ��@�B��ɒu�������Ă�����Ƃł��B����AFPGA�̃R���p�C���́ANCO����Z���Verilog�ŏ������R�[�h��

FPGA�̍ŏ��\���P�ʂ�LUT�ɒu���������Ƃ�A�`���x�����������Ȃ�悤LUT�z�u��LUT�Ԕz���̍œK����Ƃł��B

��Ɠ��e�̈Ⴂ�ŁA�v���O���~���O�����FPGA�̃R���p�C���̎��Ԃ̈Ⴂ���o�Ă��܂��B���Ȃ݂ɓ`���x��������������͓̂�����g�����グ�邽�߂ł��B

�����FPGA�̃t�@�[���E�F�A���痣��āA���M���̉�H�}���Љ�Ă����܂��I

2015�N1��18�� �L

8�y�[�W�ڂɑ���

�߂�