僆儕僕僫儖偺柍慄LAN傪FPGA偱嶌傠偆 3儁乕僕栚

夁嫀偺婰帠偼偙偪傜 1儁乕僕栚 2儁乕僕栚

1-憲怣FPGA-IQ曄挷婍

2儁乕僕栚偐傜偺偮偯偒偱偡丅FPGA偺僼傽乕儉僂僃傾傪嶌偭偰偄偒傑偡丅丅

奐敪娐嫬偑巊偄傗偡偄Altera偺FPGA傪巊梡偟傑偡丅屻弎偟傑偡偑丄Altera奐敪僣乕儖偼SignalTap嘦偲偄偆僨僶僢僈偑柍彏偱巊偊傞偺偑摿偵曋棙偱偡丅

Altera奐敪娐嫬偺僀儞僗僩乕儖曽朄偵偮偄偰偼暿偺偲偙傠偱愢柧偟傑偡丅

FPGA僼傽乕儉僂僃傾偼愭偵憲怣懁傪嶌傝傑偡丅

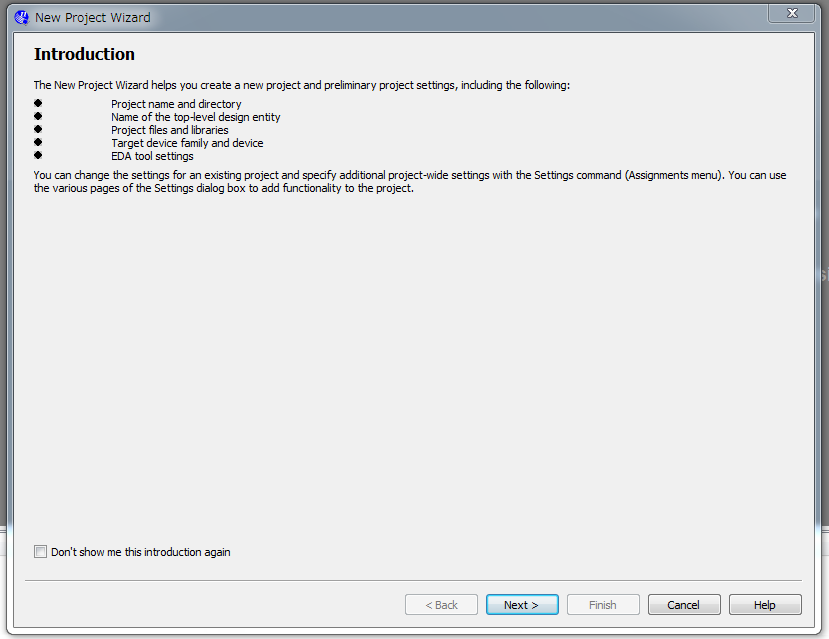

Altera偺奐敪僣乕儖偺Qurtus嘦傪婲摦偟偨傜丄傑偢偼丄僾儘僕僃僋僩傪嶌惉偟傑偡丅

儊僀儞儊僯儏乕丂仺丂File 仺丂New Project Wizard丂偱僾儘僕僃僋僩嶌惉僂傿僓乕僪偑奐偒傑偡丅

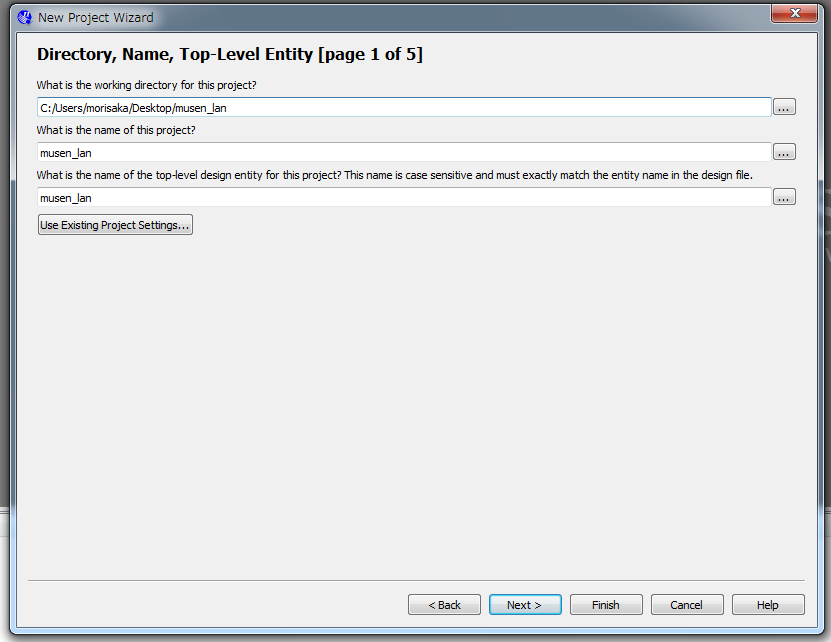

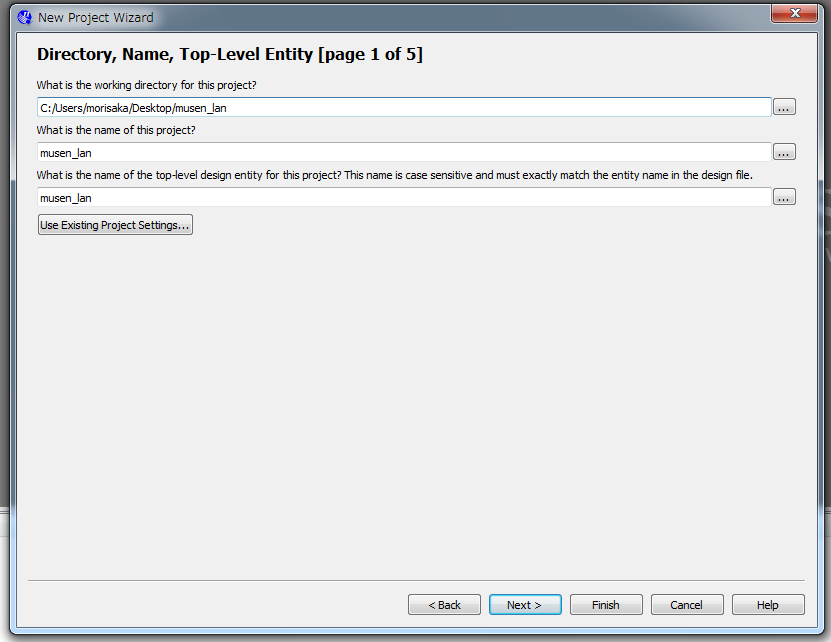

Next傪僋儕僢僋偡傞偲丄僾儘僕僃僋僩柤偲嶌惉僨傿儗僋僩儕傪巜掕偡傞夋柺偑奐偒傑偡丅

僾儘僕僃僋僩柤偼"musen_lan"偵偟偰丄僨僗僋僩僢僾偵"musen_lan"偲偄偆僨傿儗僋僩儕傪嶌惉偟偰偍偄偰僾儘僕僃僋僩偺曐懚応強偵偟傑偟偨丅

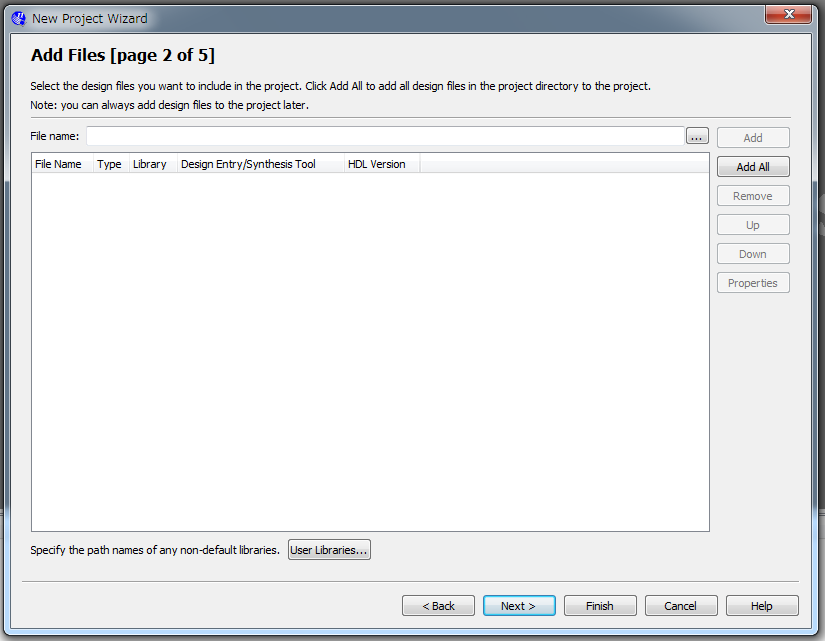

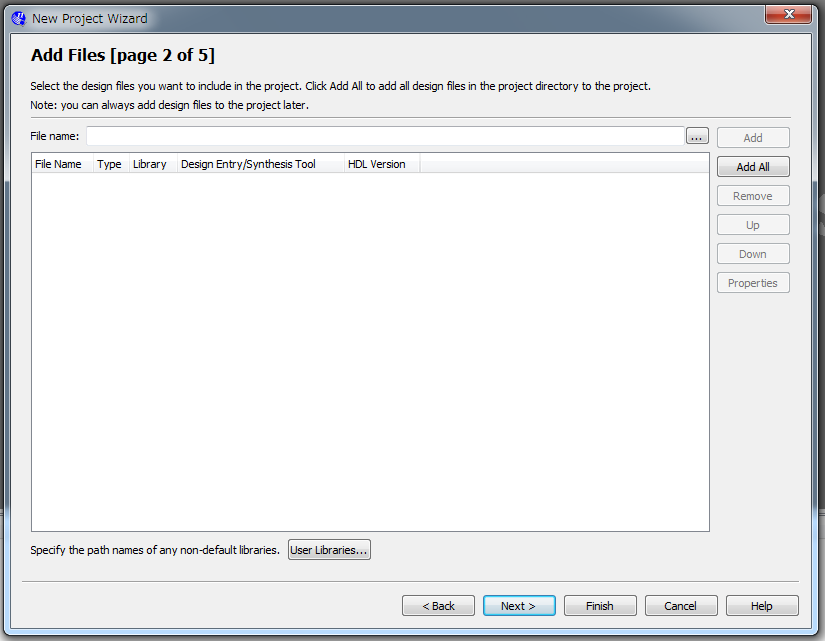

Next傪僋儕僢僋偡傞偲丄僾儘僕僃僋僩偵捛壛偡傞僼傽僀儖傪巜掕偡傞夋柺偑奐偒傑偡丅

摿偵捛壛偡傞僼傽僀儖偼偁傝傑偣傫偺偱丄壗傕偣偢偵Next傪僋儕僢僋偟傑偡丅師偼FPGA宆柤傪巜掕偡傞夋柺偑奐偒傑偡丅

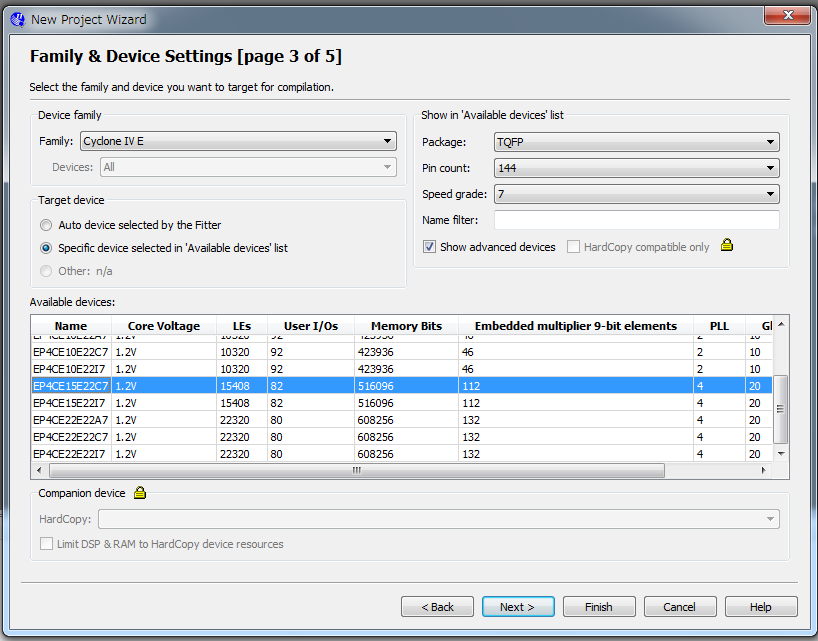

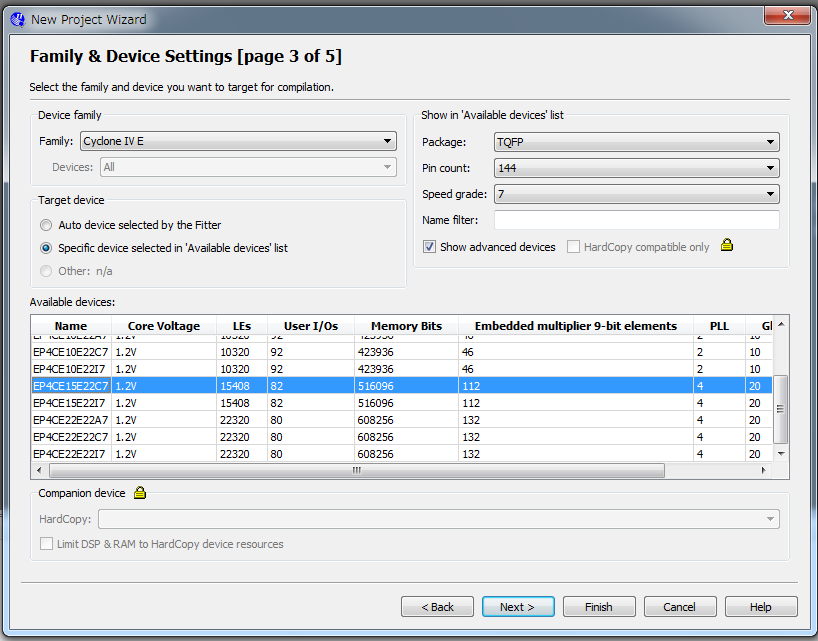

EP4CE15E22C7偲偄偆Cyclone4僔儕乕僘偺QFP144僷僢働乕僕偺僗僺乕僪僌儗乕僪俈偺僨僶僀僗傪慖戰偟傑偡丅

FPGA偺宆柤偼屻偱曄峏偡傞偙偲傕壜擻偱偡丅

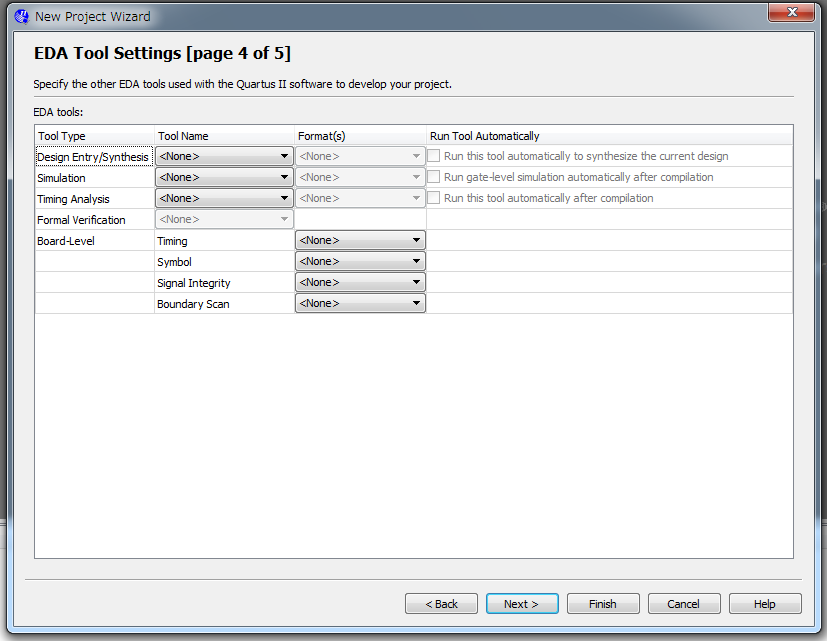

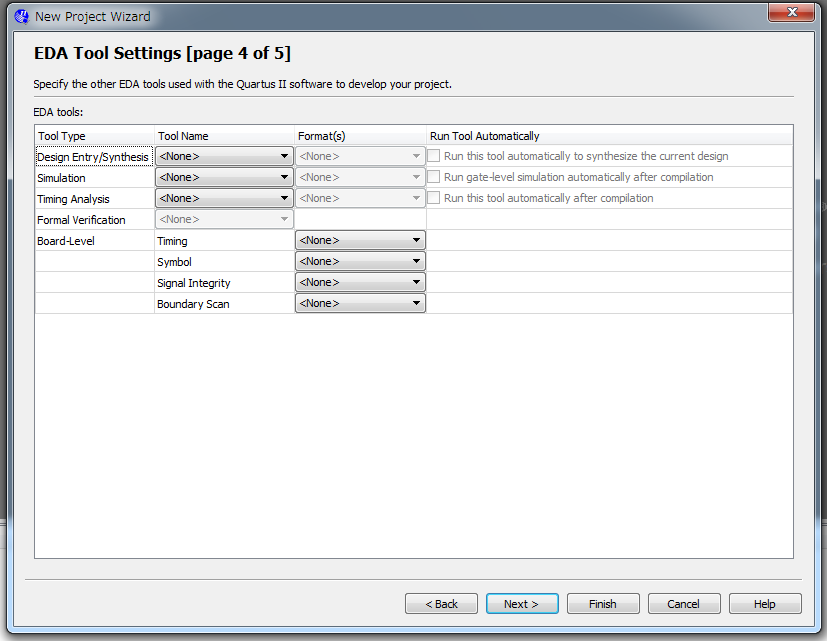

Next傪僋儕僢僋偡傞偲丄EDA僣乕儖偺愝掕夋柺偑奐偒傑偡丅

摿偵愝掕偼偁傝傑偣傫偺偱丄壗傕偣偢偵Next傪僋儕僢僋偟傑偡丅嵟屻偵僾儘僕僃僋僩偺僒儅儕乕偑昞帵偝傟傑偡丅

Finish傪僋儕僢僋偟偰僾儘僕僃僋僩嶌惉僂傿僓乕僪偼姰椆偱偡丅

FPGA偺僼傽乕儉偼Verilog-RTL傗VHDL偺僐乕僪偱嶌惉偡傞働乕僗偑懡偄偱偡偑丄崱夞偼夞楬恾傪儊僀儞偵偟偰僼傽乕儉傪嶌惉偟偰偄偒傑偡丅

夞楬恾偩偲僼傽乕儉慡懱偺峔惉偑傂偲栚偱尒偰棟夝偡傞偡傞偙偲偑偱偒傑偡丅

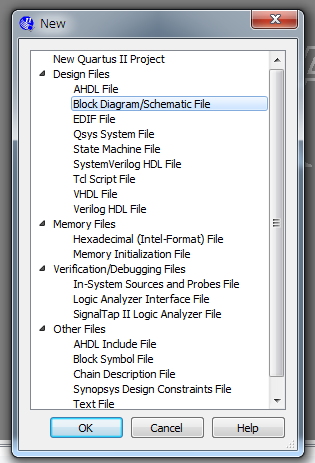

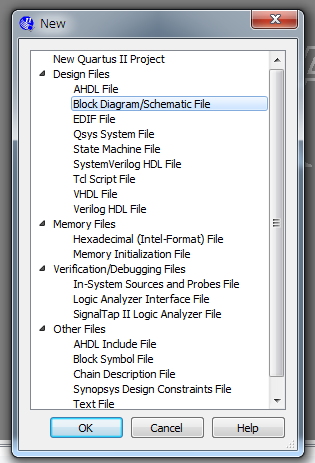

傑偢偼夞楬恾傪怴婯嶌惉偟傑偡丅儊僀儞儊僯儏乕丂仺丂File 仺丂New丂偱怴婯僼傽僀儖嶌惉夋柺偑奐偒傑偡丅

僼傽僀儖庬暿偺堦棗偐傜 Block Diagram / Schematic File 傪慖傇偲丄怴婯夞楬恾偑嶌惉偝傟傑偡丅

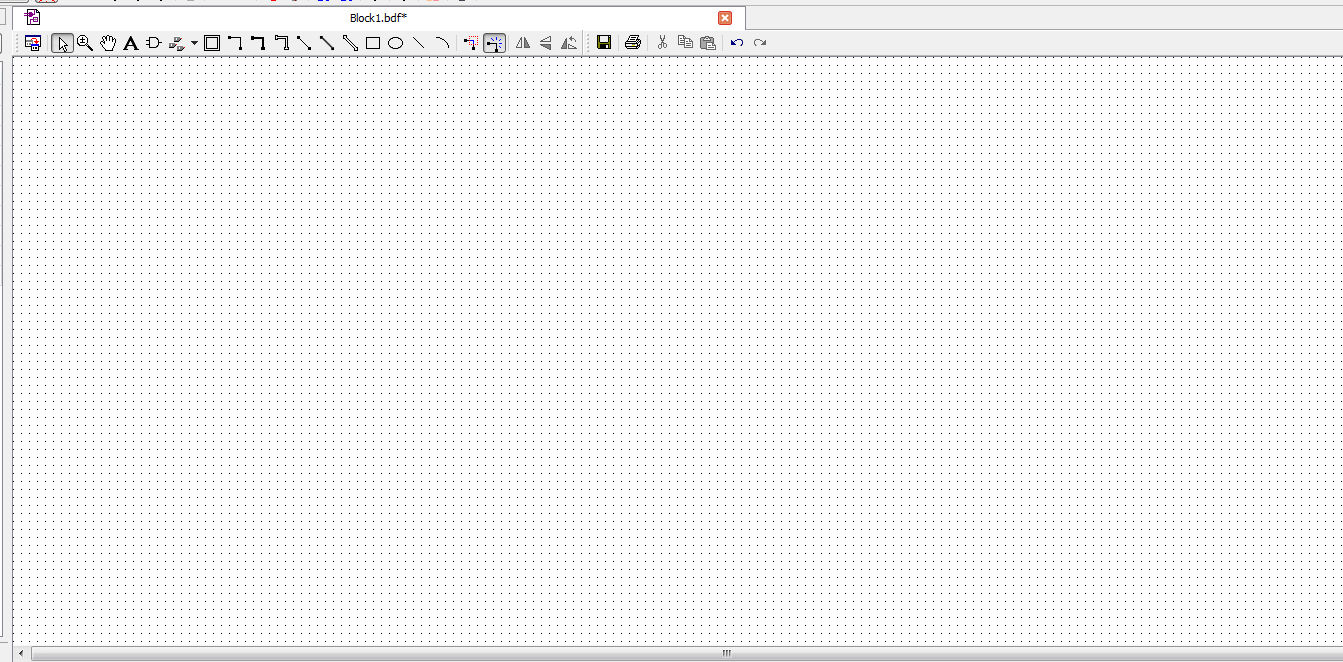

夞楬恾偼摍娫妘偵揰偑暲傫偩傕偺偱偡丅

夞楬恾偵慜暸偺IQ曄挷婍偲摨偠傕偺傪嶌偭偰偄偒傑偡丅

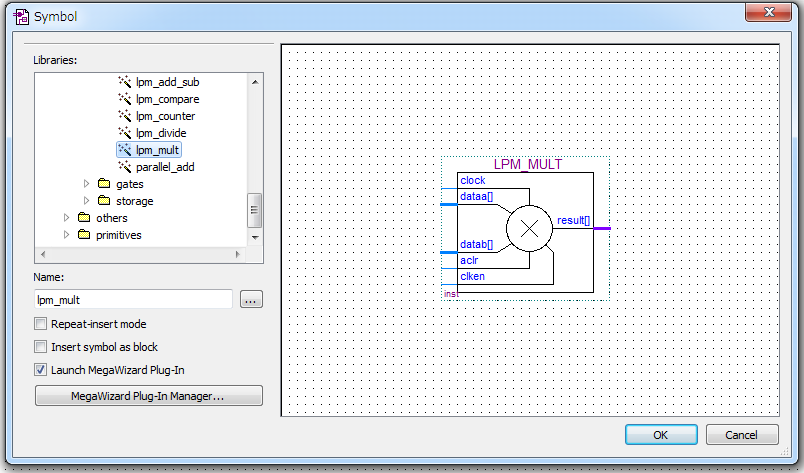

傑偢偼忔嶼婍傪嶌傝傑偡丅夞楬恾忋偵儅僂僗億僀儞僞傪帩偭偰偒偰嵍僟僽儖僋儕僢僋偡傞偲僔儞儃儖嶌惉夋柺偑奐偒傑偡丅

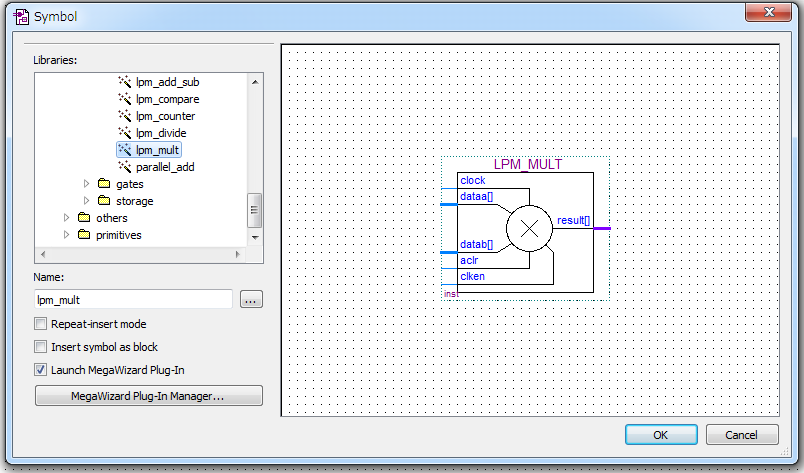

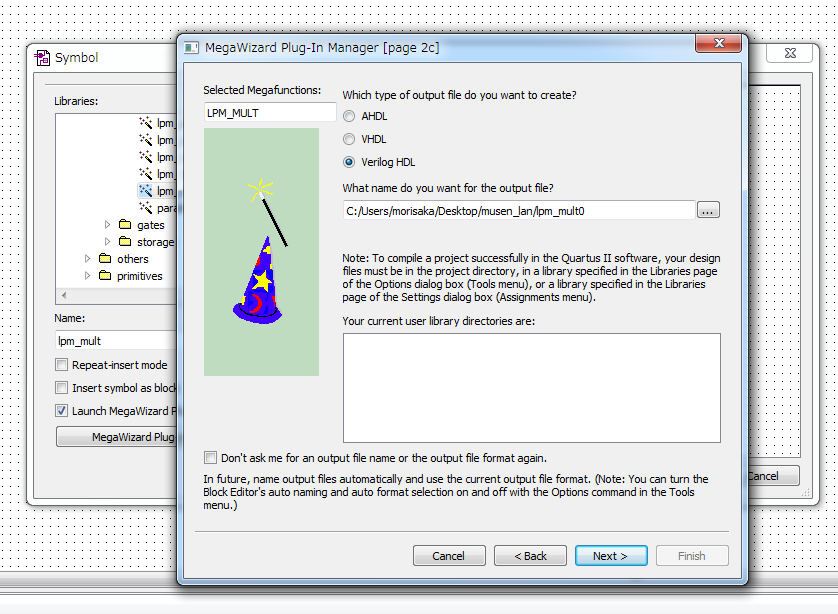

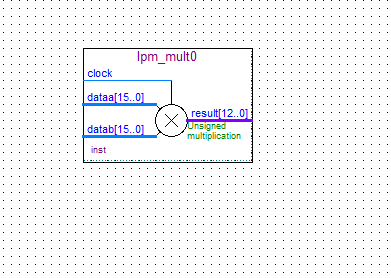

僔儞儃儖堦棗偐傜libraries仺arithmetic仺lpm_mult傪慖戰偡傞偲忔嶼婍偺徻嵶僷儔儊乕僞愝掕夋柺偑奐偒傑偡丅

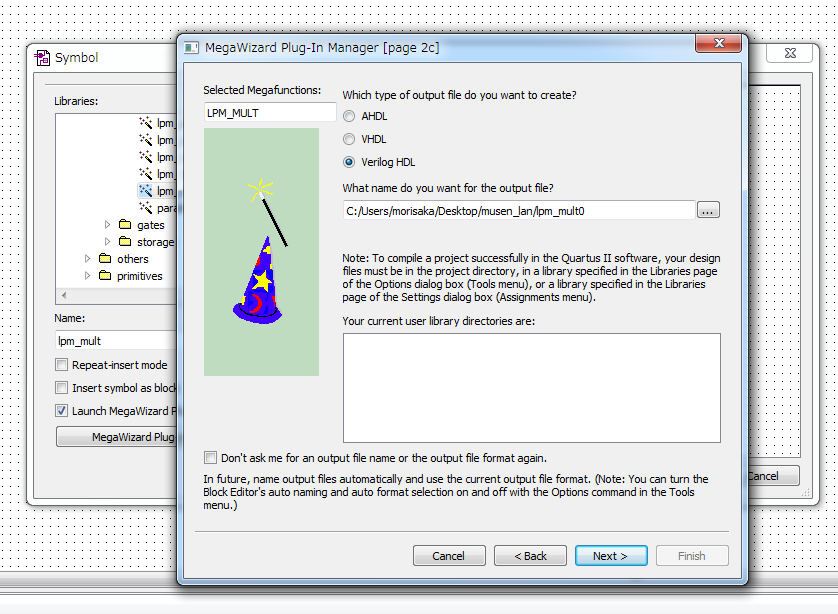

嶌惉偡傞忔嶼婍偵柤慜傪偮偗傑偡丅僼傽乕儉僂僃傾偵傛偭偰偼庬椶偺堘偆暋悢偺忔嶼婍傪巊梡偡傞偙偲傕偁傝傑偡偐傜柤慜傪偮偗偰嬫暿偟傑偡丅

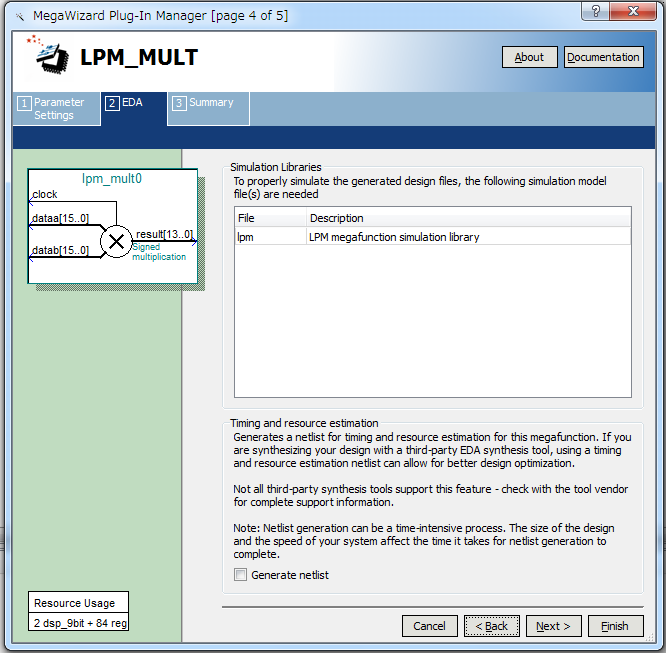

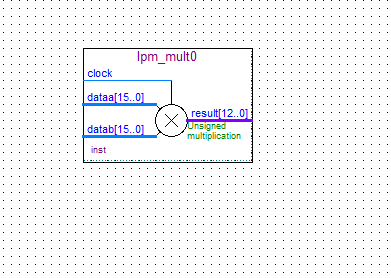

僨僼僅儖僩偺lpm_multi0偺傑傑偱戝忎晇偱偡偐傜Next傪僋儕僢僋偟傑偡丅師偵價僢僩暆愝掕夋柺偑弌偰偒傑偡丅

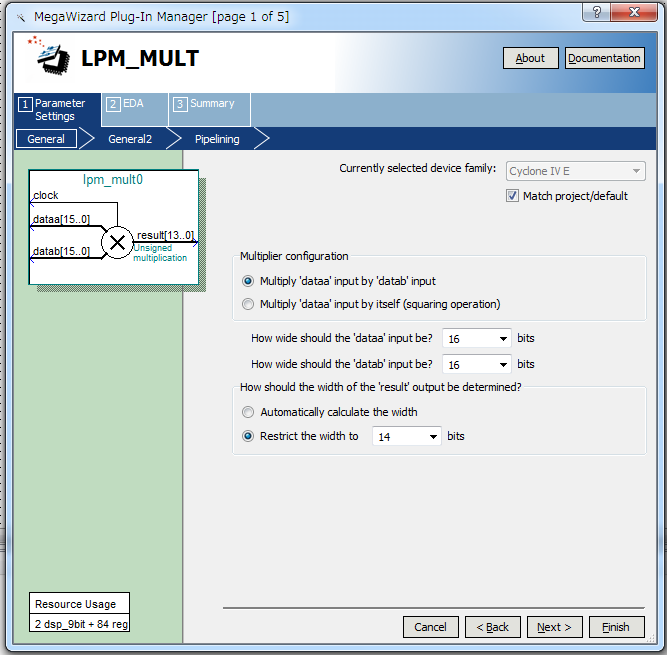

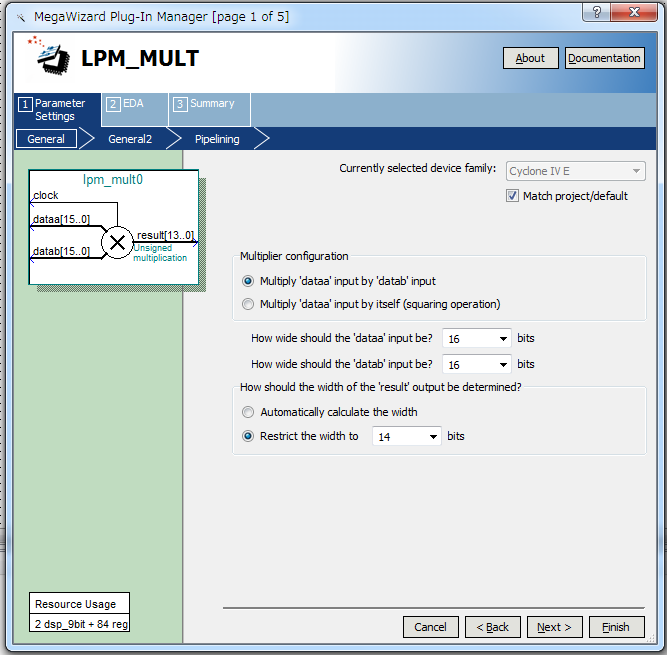

AxB(捠忢偺忔嶼)偐丄AxA乮2忔乯偐偺慖戰偼丄捠忢偺忔嶼傪慖傫偱丄擖椡價僢僩暆偼A,B偲傕偵16價僢僩偵丄弌椡價僢僩暆偼14價僢僩傪慖傃傑偡丅

16價僢僩x16價僢僩偺忔嶼偺弌椡偼32價僢僩偱偡偑丄壓埵18價僢僩偼忔嶼婍撪晹偱幪偰偰14價僢僩弌椡偲偟傑偡丅

忔嶼婍偺屻抜偱32價僢僩偺惛搙偼昁梫偁傝傑偣傫偺偱丄忔嶼婍偺弌椡偱壓埵價僢僩傪幪偰偰偟傑偄傑偡丅

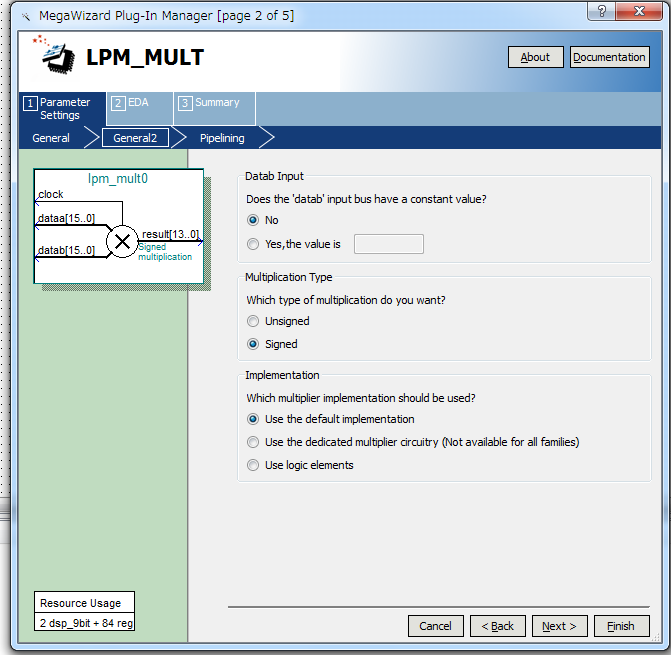

Next傪僋儕僢僋偡傞偲師偺僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

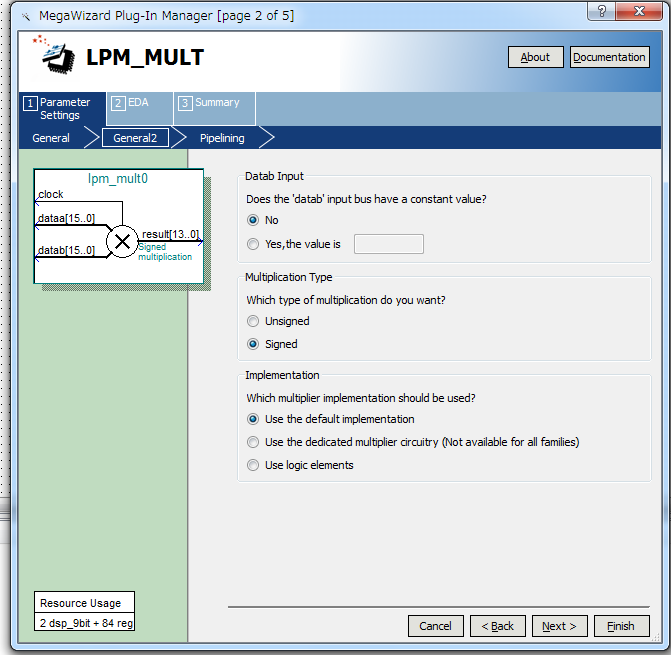

B擖椡傪曄悢偵偡傞偐掕悢偵偡傞偐偼曄悢傪慖戰偟丄晞崋晅偒偐晞崋側偟偐偼晞崋晅偒傪慖戰偟丄僀儞僾儕儊儞僥乕僔儑儞偼僨僼僅儖僩傪慖戰偟傑偡丅

晞崋晅偒偵偮偄偰彮偟曗懌偟傑偡偲丄2偺曗悢傪巊梡偟傑偡丅

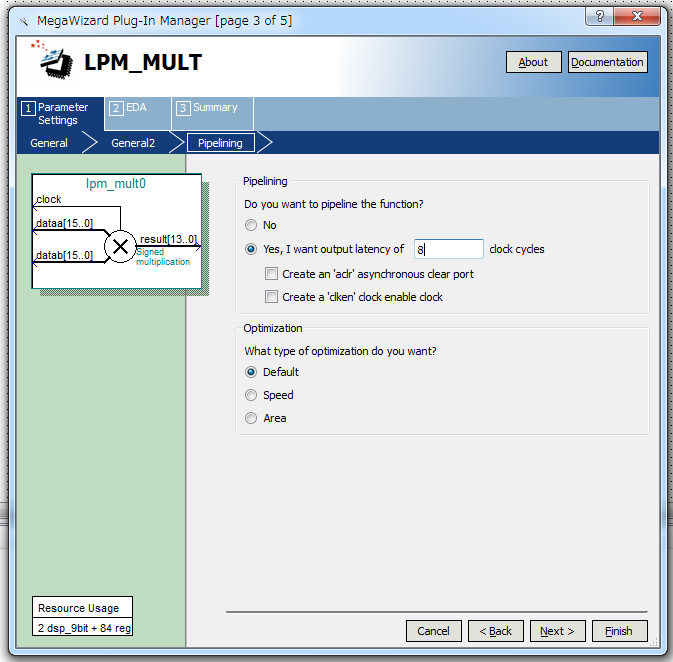

Next傪僋儕僢僋偡傞偲師偺僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

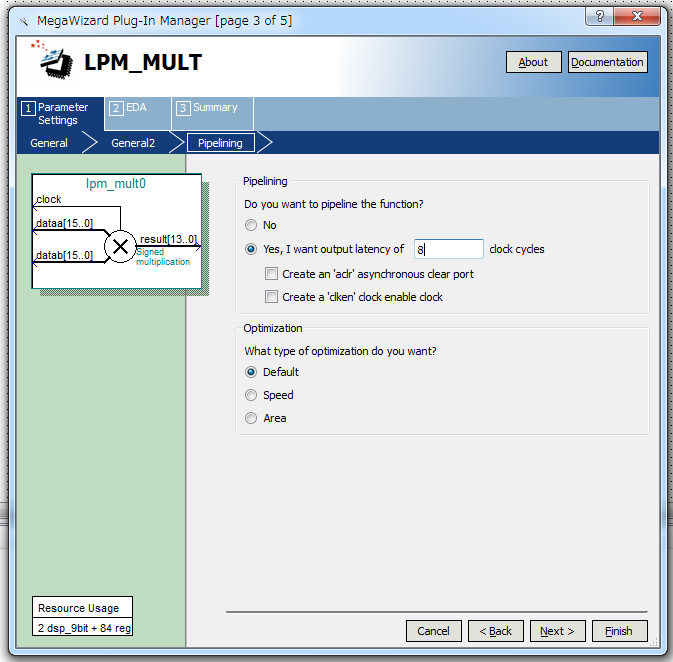

僷僀僾儔僀儞偼俉抜僷僀僾儔僀儞偵愝掕偟偰aclr偲clken偺僠僃僢僋儃僢僋僗偼偼偢偟偰偍偒傑偡丅嵟揔壔偼僨僼僅儖僩傪慖戰偟傑偡丅

僷僀僾儔僀儞偲偼丄忔嶼寢壥偑弌傞傑偱偵暋悢僋儘僢僋僒僀僋儖傪梫偡傞傛偆側夞楬峔惉偺偙偲偱偡丅

僷僀僾儔僀儞抜悢傪憹傗偡傎偳偵寢壥偑弌傞傑偱偺僋儘僢僋僒僀僋儖悢偼憹偊傑偡偑丄嵟崅摦嶌廃攇悢偼偁偑傝傑偡丅

僼傽乕儉僂僃傾慡懱偺嵟崅摦嶌廃攇悢偵懳偟偰忔嶼婍偺摦嶌廃攇悢偑儃僩儖僱僢僋偵側傞働乕僗偑懡偄偺偱偡偑丄

偙偺応崌偵偼忔嶼婍傪僷僀僾儔僀儞壔偡傞偙偲偱嵟崅廃攇悢偺栤戣傪夝寛偱偒傞応崌偑偁傝傑偡丅

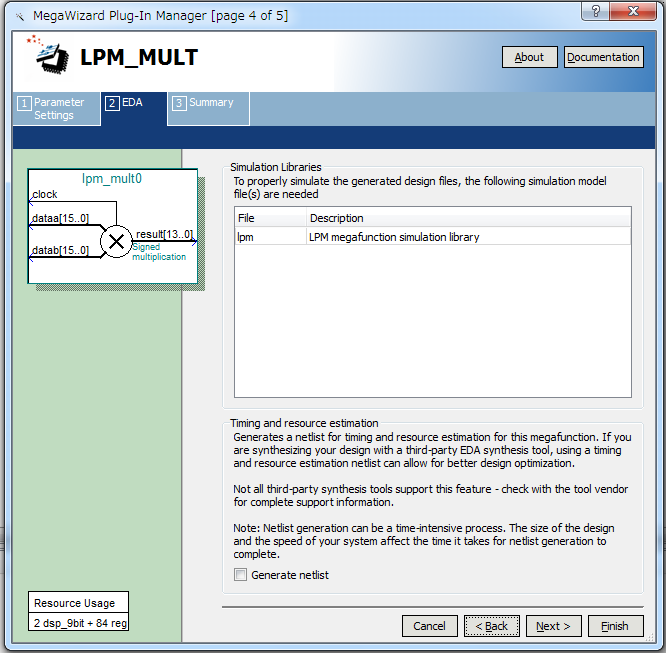

Next傪僋儕僢僋偡傞偲師偺愝掕夋柺偑奐偒傑偡丅

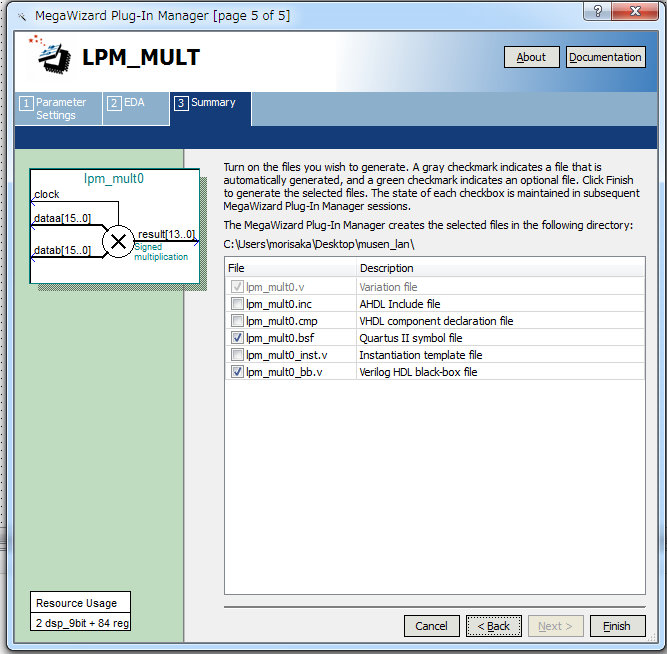

僔儈儏儗乕僔儑儞愝掕偼壗傕曄偊偢偵Next傪僋儕僢僋偟傑偡丅

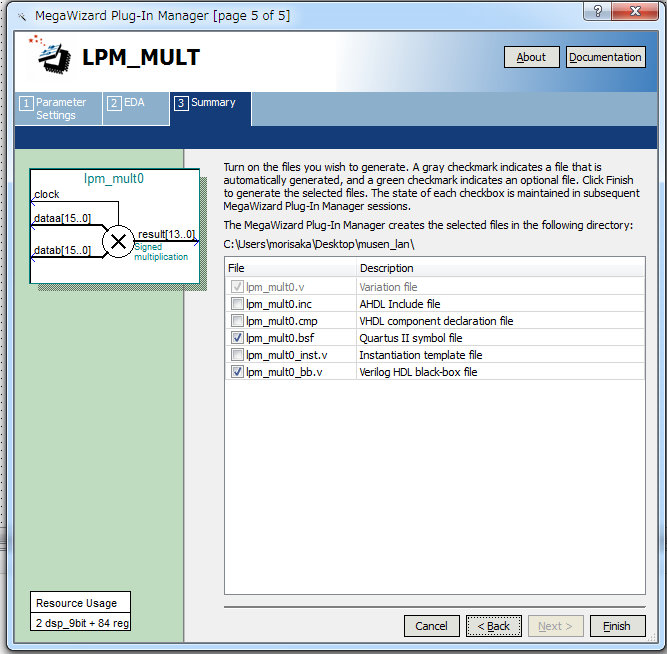

僒儅儕乕傕摿偵壗傕曄偊偢偵Finish傪僋儕僢僋偟傑偡丅忔嶼婍偑嶌惉偝傟偰夞楬恾偵忔嶼婍偑捛壛偝傟傑偡丅

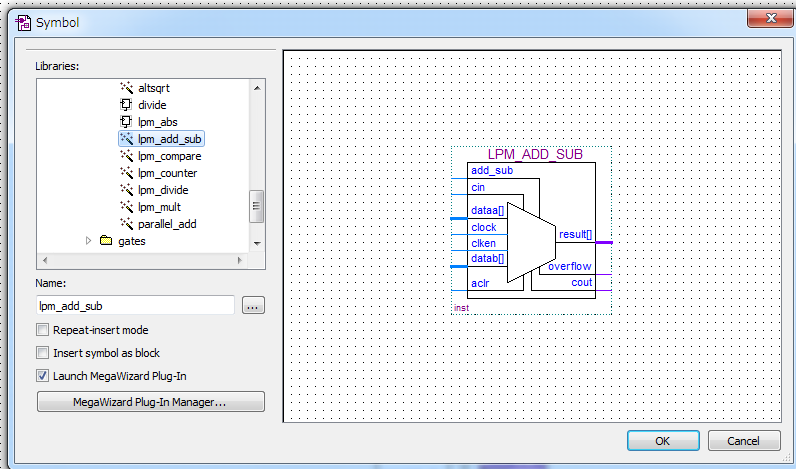

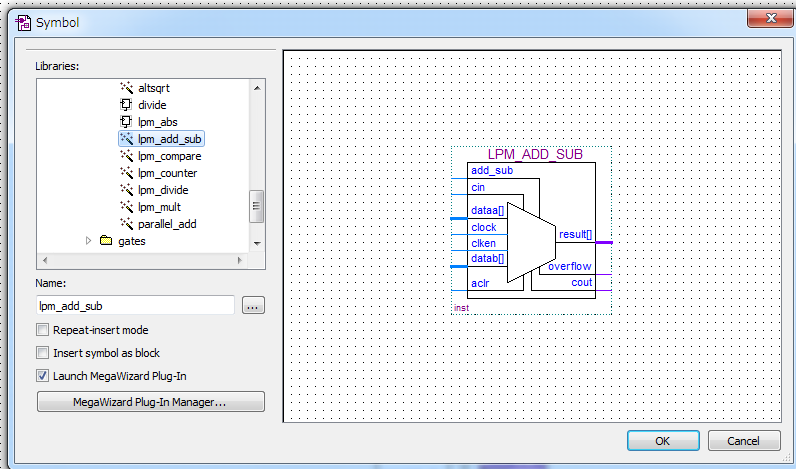

師偵壛嶼婍傪嶌傝傑偡丅忔嶼婍偺帪偲摨偠傛偆偵夞楬恾忋偵儅僂僗億僀儞僞傪帩偭偰偒偰嵍僟僽儖僋儕僢僋偡傞偲僔儞儃儖嶌惉夋柺偑奐偒傑偡丅

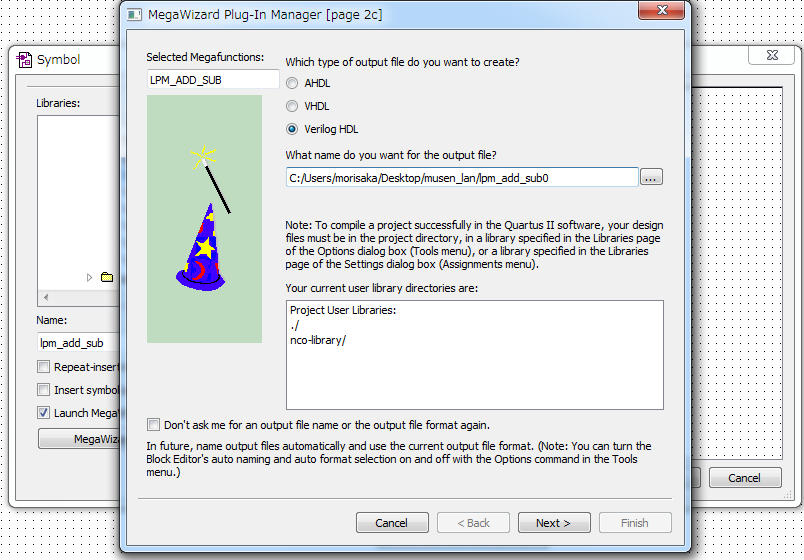

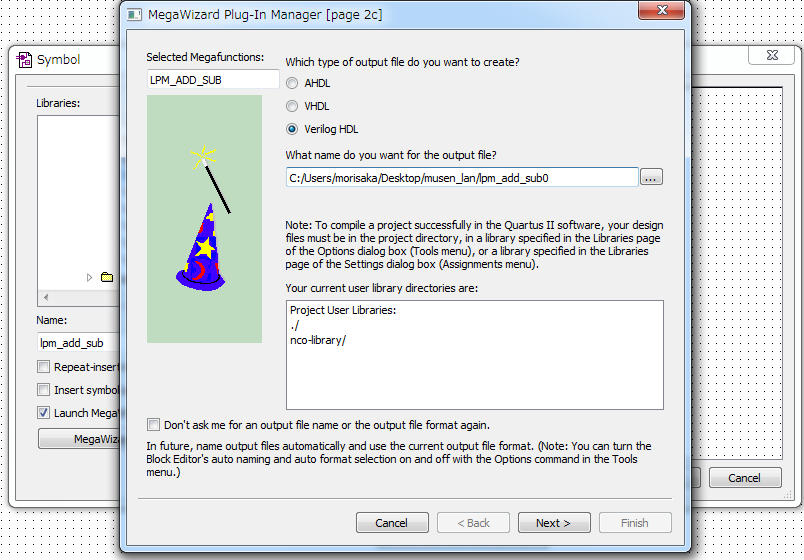

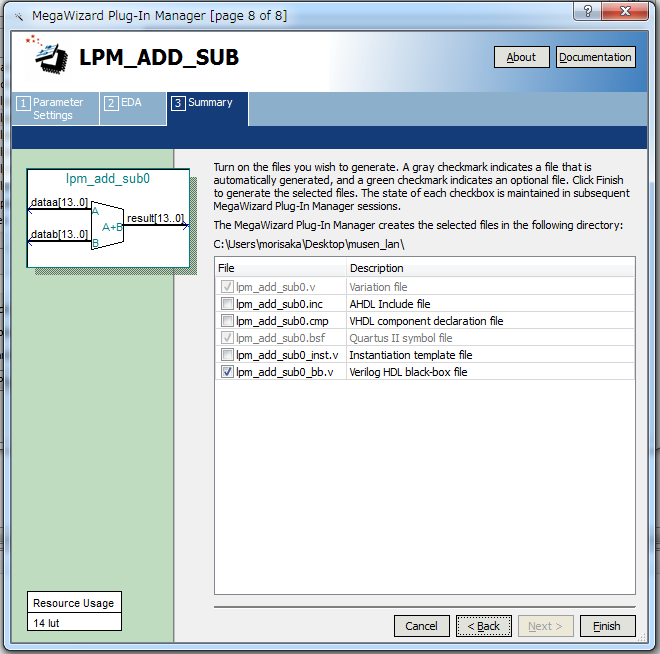

僔儞儃儖堦棗偐傜libraries仺arithmetic仺lpm_add_sub傪慖戰偡傞偲壛尭嶼婍偺徻嵶僷儔儊乕僞愝掕夋柺偑奐偒傑偡丅

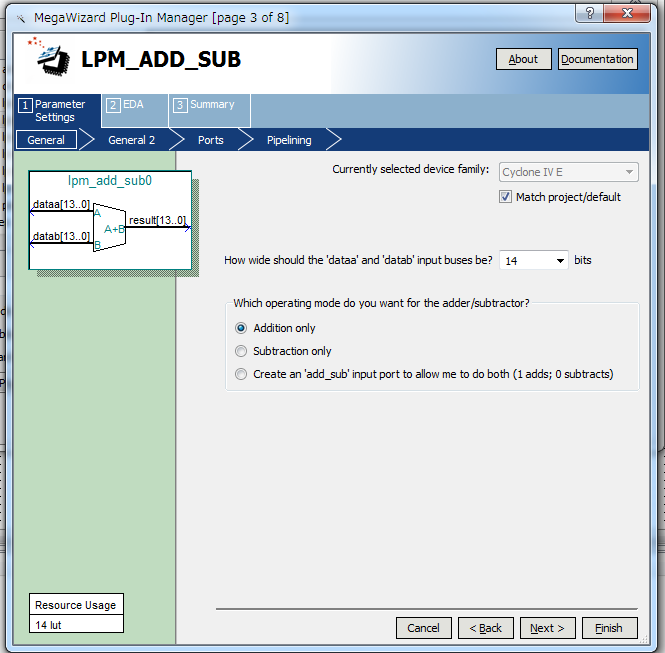

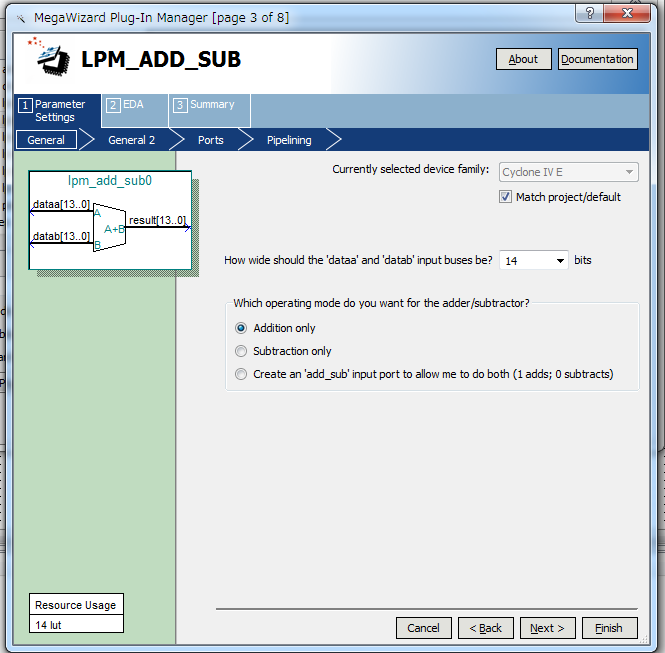

壛嶼婍偺柤慜偼僨僼僅儖僩偺lpm_add_sub0偺傑傑偱戝忎晇偱偡偐傜Next傪僋儕僢僋偟傑偡丅師偵價僢僩暆偲壛尭嶼偺愝掕夋柺偑弌偰偒傑偡丅

價僢僩暆偼14偵偟偰丄壛嶼丒尭嶼丒壛尭嶼偺庬暿偼壛嶼傪慖戰偟傑偡丅

價僢僩暆偼擖椡丒弌椡偳偪傜傕14價僢僩偱偡偺偱丄弌椡偑儘乕儖僆乕僶乕偡傞応崌偑偁傝傑偡丅儘乕儖僆乕僶乕偟側偄傛偆偵巊梡偟傑偡丅

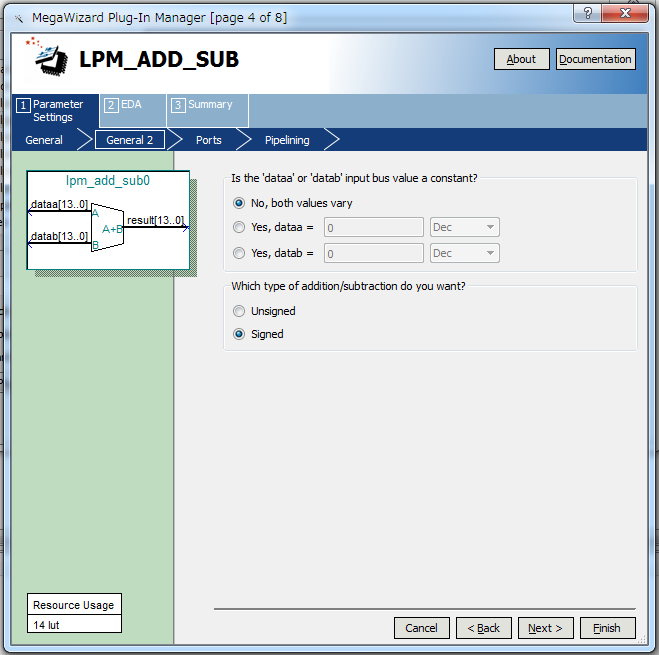

Next傪僋儕僢僋偡傞偲師偺僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

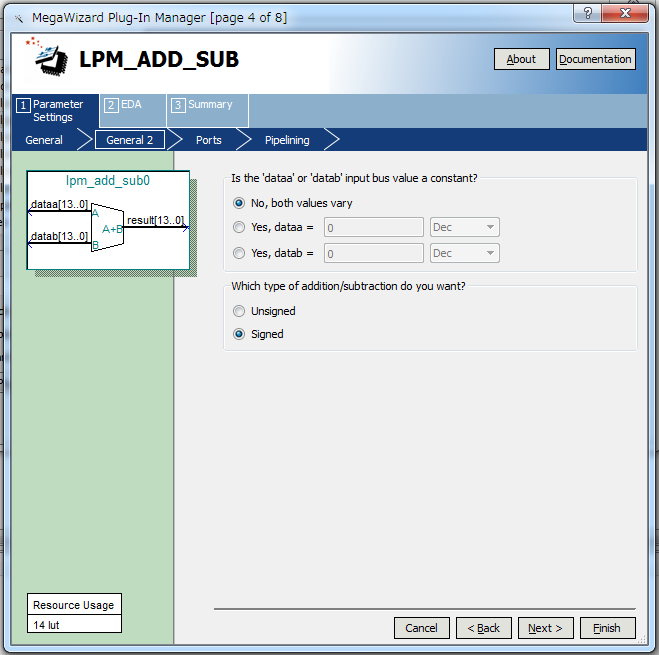

曄悢亄曄悢偐丄掕悢亄曄悢偐丄曄悢亄掕悢偐偼丄曄悢亄曄悢傪慖戰偟傑偡丅晞崋側偟偐晞崋晅偒偐偼丄晞崋晅偒傪慖戰偟傑偡丅

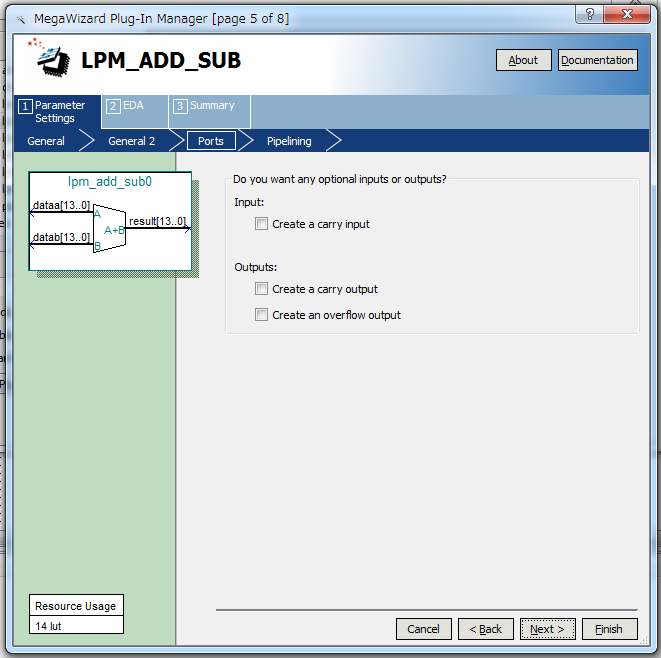

Next傪僋儕僢僋偡傞偲師偺僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

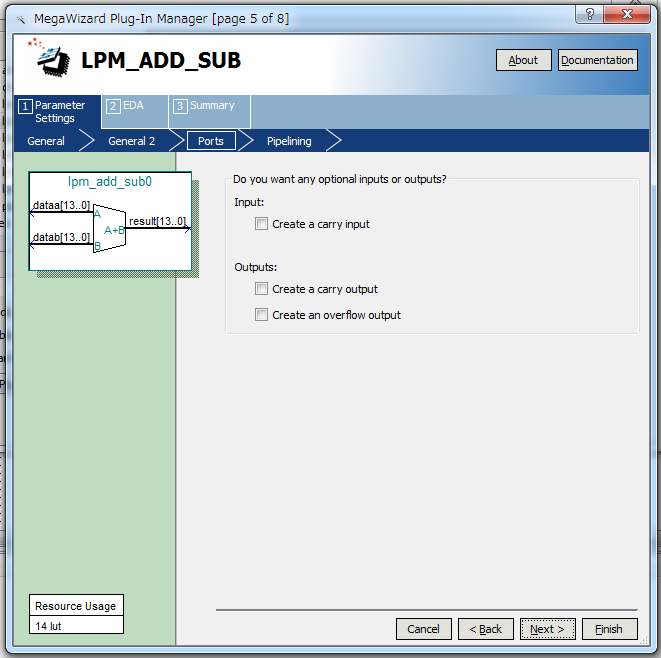

僉儍儕乕僀儞丄僉儍儕乕傾僂僩丄僆乕僶乕僼儘乕僼儔僌偼崱夞偼巊梡偟傑偣傫丅

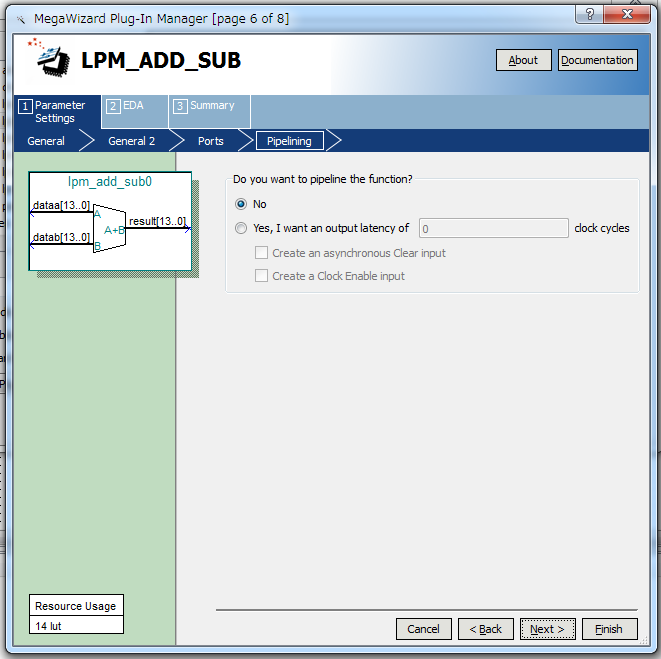

Next傪僋儕僢僋偡傞偲師偺僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

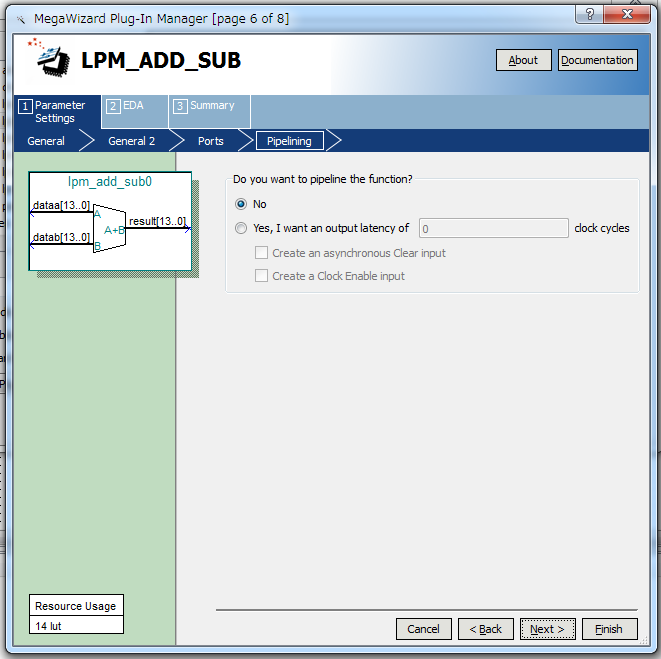

壛嶼婍偼僷僀僾儔僀儞峔惉偵偼偟傑偣傫丅

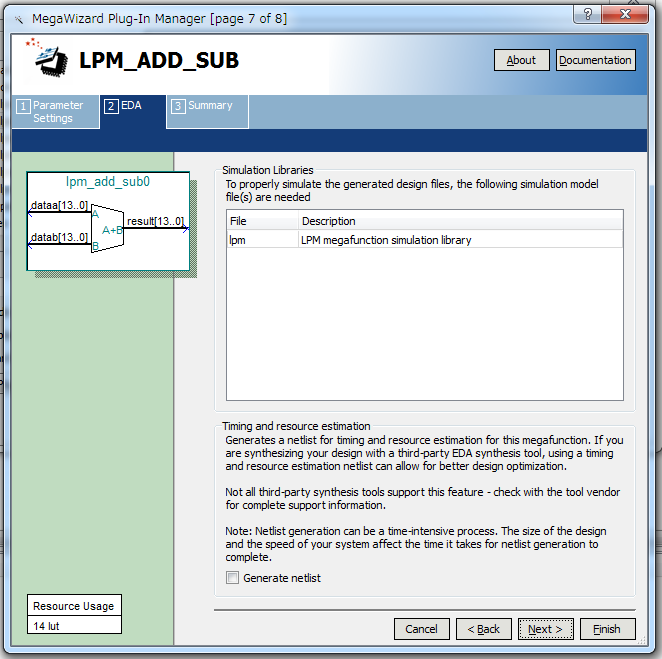

Next傪僋儕僢僋偡傞偲師偺僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

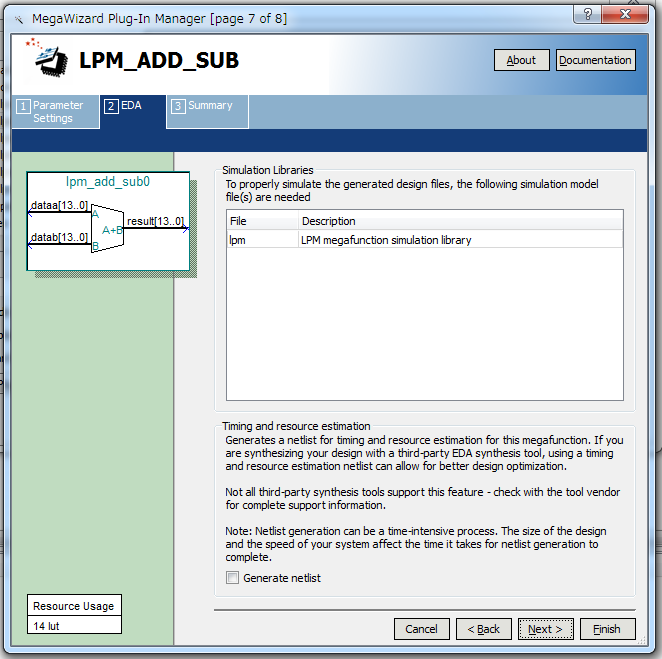

僔儈儏儗乕僔儑儞愝掕偼壗傕曄偊偢偵Next傪僋儕僢僋偟傑偡丅

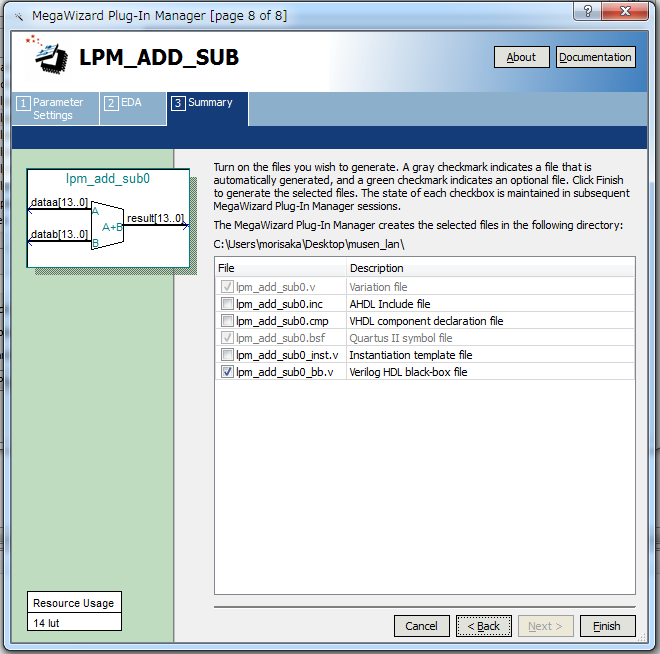

僒儅儕乕傕摿偵壗傕曄偊偢偵Finish傪僋儕僢僋偟傑偡丅壛嶼婍偑嶌惉偝傟偰夞楬恾偵忔嶼婍偑捛壛偝傟傑偡丅

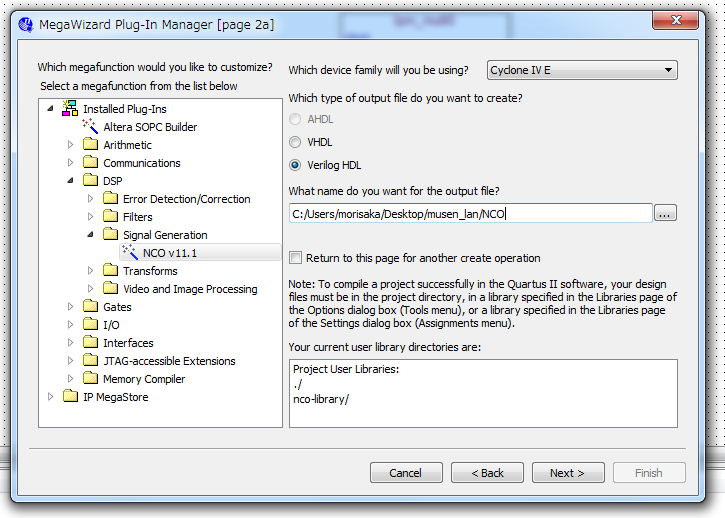

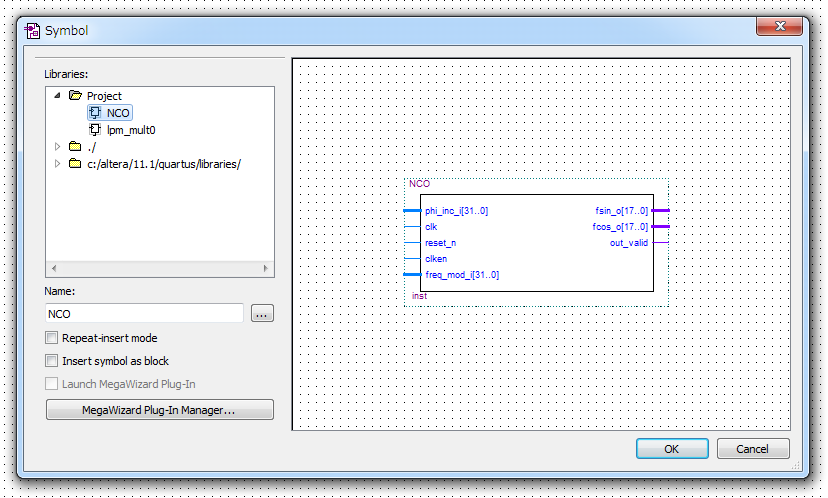

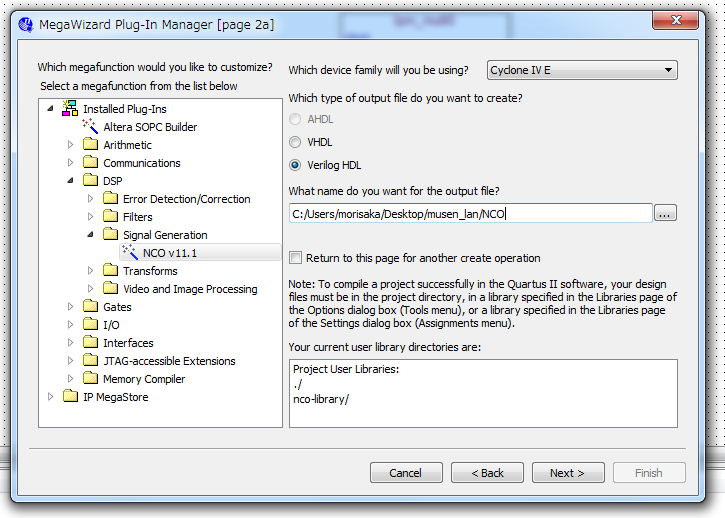

師偵10MHz敪怳婍(NCO)傪嶌傝傑偡丅忔嶼婍丒壛嶼婍偲嶌傝曽偑彮偟堘偄傑偡丅儊僀儞儊僯儏乕丂仺丂Tools 仺丂MegaWizard Plug-In Manager 偱怴婯儌僕儏乕儖嶌惉夋柺偑奐偒傑偡丅

儌僕儏乕儖堦棗偐傜DSP仺Signal Generation仺NCO v11.1傪慖傃傑偡丅柤慜偼NCO偵偟傑偡丅

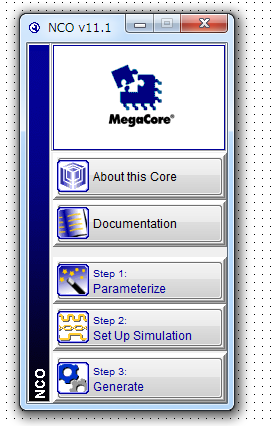

Next傪僋儕僢僋偡傞偲NCO僂傿僓乕僪偑弌偰偒傑偡丅

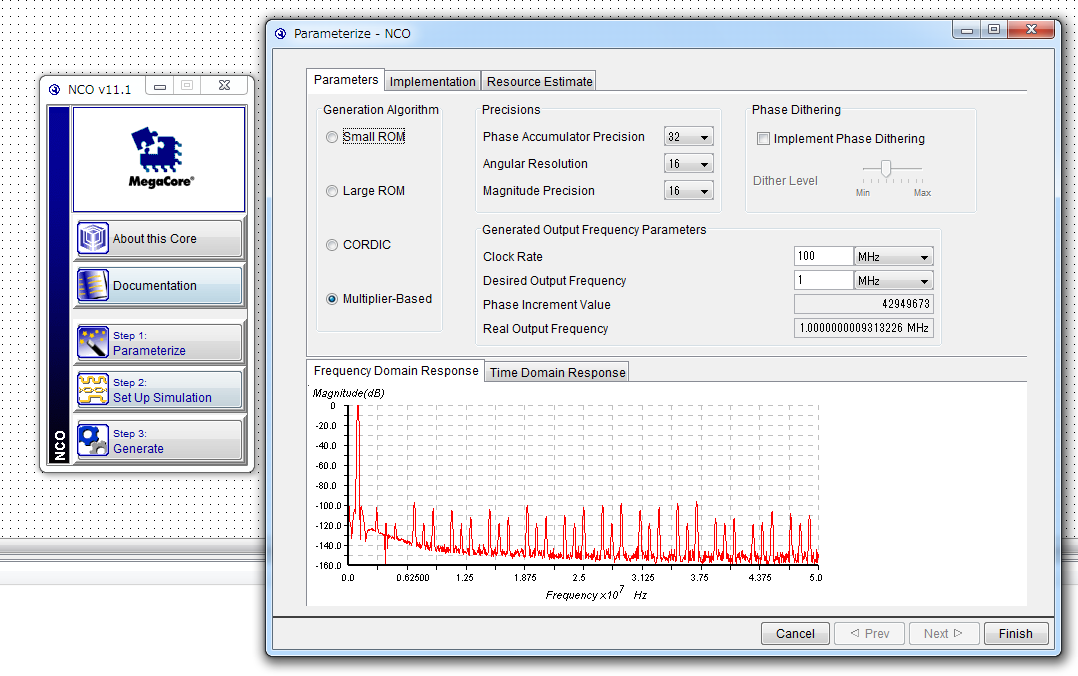

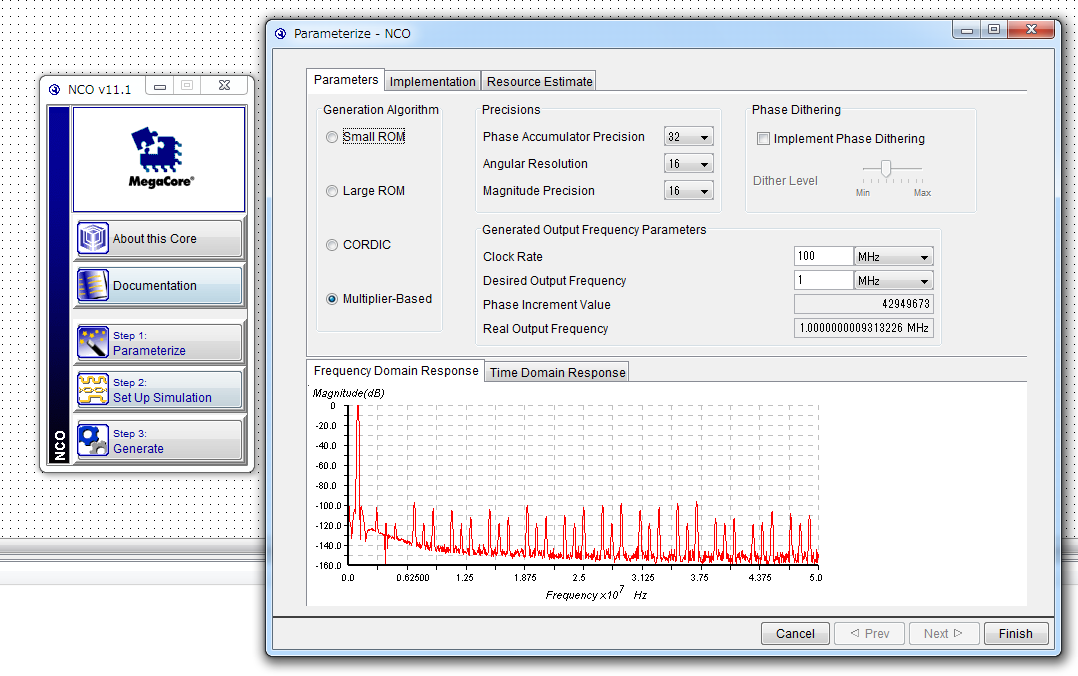

Step1 Parameterize傪僋儕僢僋偡傞偲丄僷儔儊乕僞愝掕夋柺偑弌偰偒傑偡丅

Parameters僞僽傪奐偄偰丄Generation偼Algorithm偼Multiplier-Based傪丄Precision偼忋偐傜弴偵32丒16丒16傪丄PhaseDithering柍偟傪愝掕偟傑偡丅

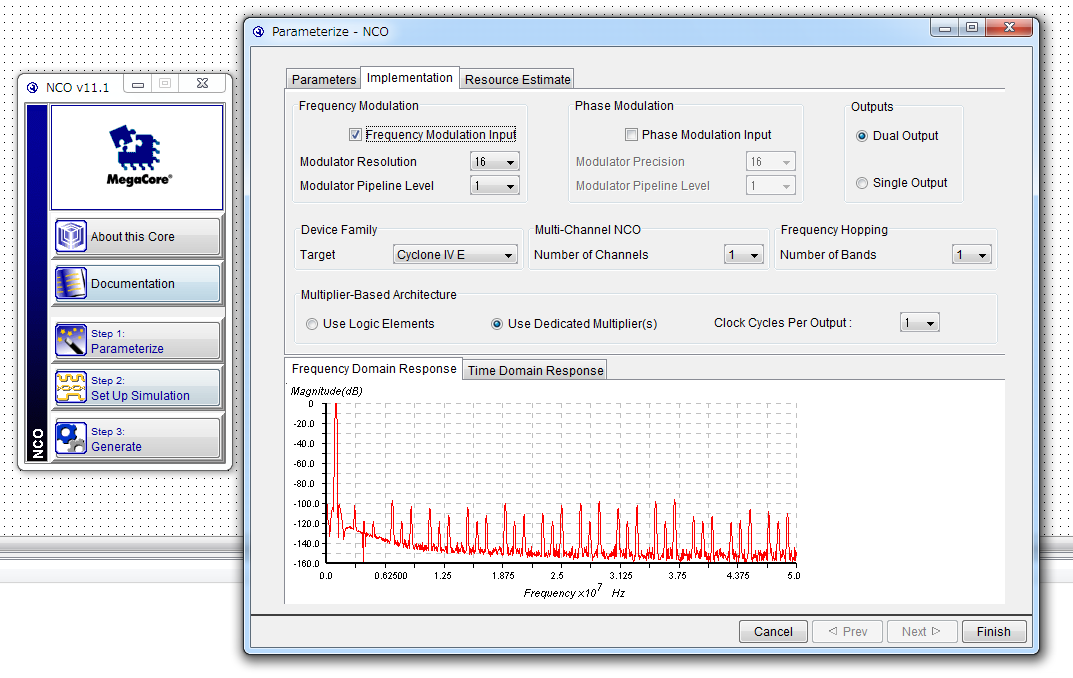

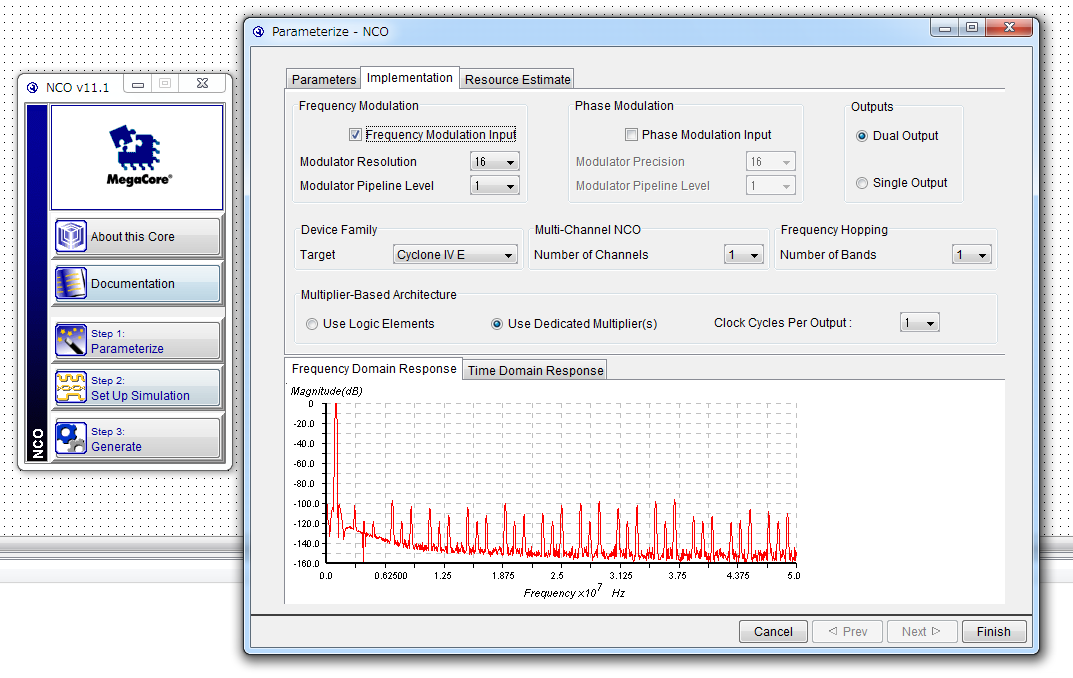

Implementation僞僽傪奐偄偰丄Frequency Modulation偁傝偺16價僢僩傪丄Phase Modulation側偟丄Outputs偼Dual Output傪愝掕偟傑偡丅

懠崁栚偼僨僼僅儖僩偱OK偱偡丅

忋婰偺僂傿僓乕僪偺Step2 Set Upp Simulation偼摿偵愝掕偼偁傝傑偣傫丅

Step3 Generate傪僋儕僢僋偟偰NCO傪惗惉偟傑偡丅

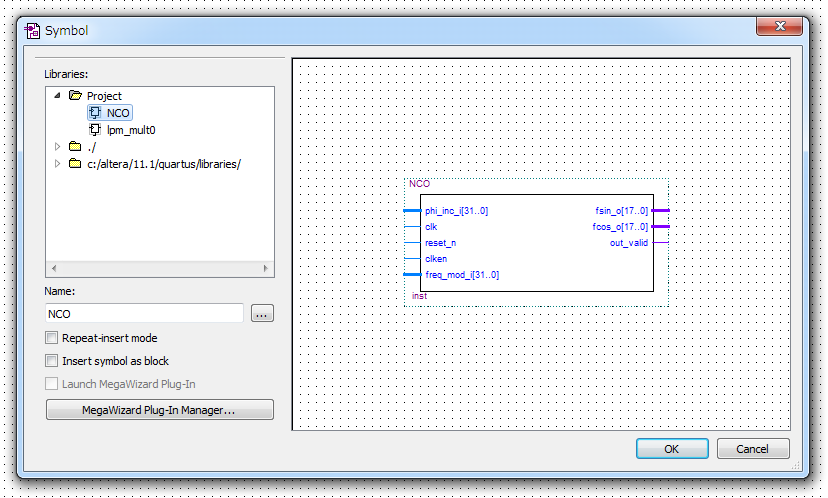

NCO傪惗惉姰椆偟偨傜丄夞楬恾偱嵍僟僽儖僋儕僢僋偡傞偲丄僔儞儃儖堦棗偵愭傎偳嶌偭偨NCO偑壛傢偭偰偄傑偡偐傜丄NCO傪慖戰偟偰夞楬恾偵捛壛偟傑偡丅

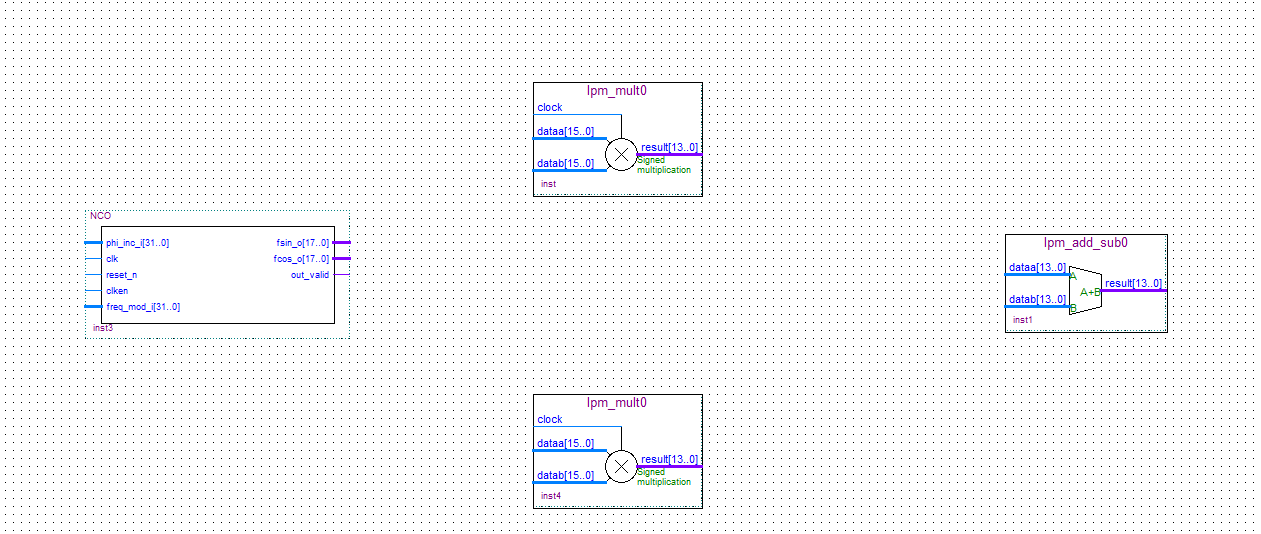

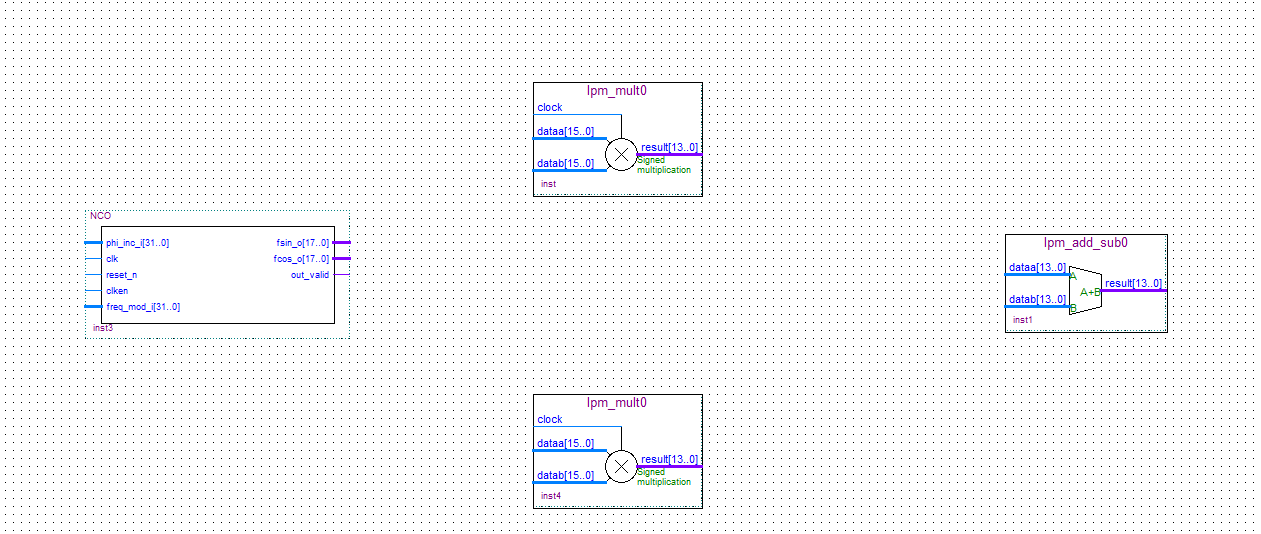

忔嶼婍丒壛嶼婍丒敪怳婍傪嶌惉偟偰夞楬恾偵攝抲偟偨條巕偱偡丅忔嶼婍偼俀屄巊偄傑偡偐傜丄侾屄嶌偭偨傜僐僺儁偟偰偔偩偝偄丅

師夞偼丄憲怣FPGA偵昁梫側婡擻傪堷偒懕偒嶌偭偰偄偒傑偡両

2015擭1寧9擔 婰

4儁乕僕栚偵懕偔

栠傞