オリジナルの無線LANをFPGAで作ろう 5ページ目

過去の記事はこちら 1ページ目 2ページ目 3ページ目 4ページ目

1-送信FPGA-IQ変調器と低速ADCのインターフェース回路

4ページ目からのつづきです。FPGAのファームウェアを作っていきます。

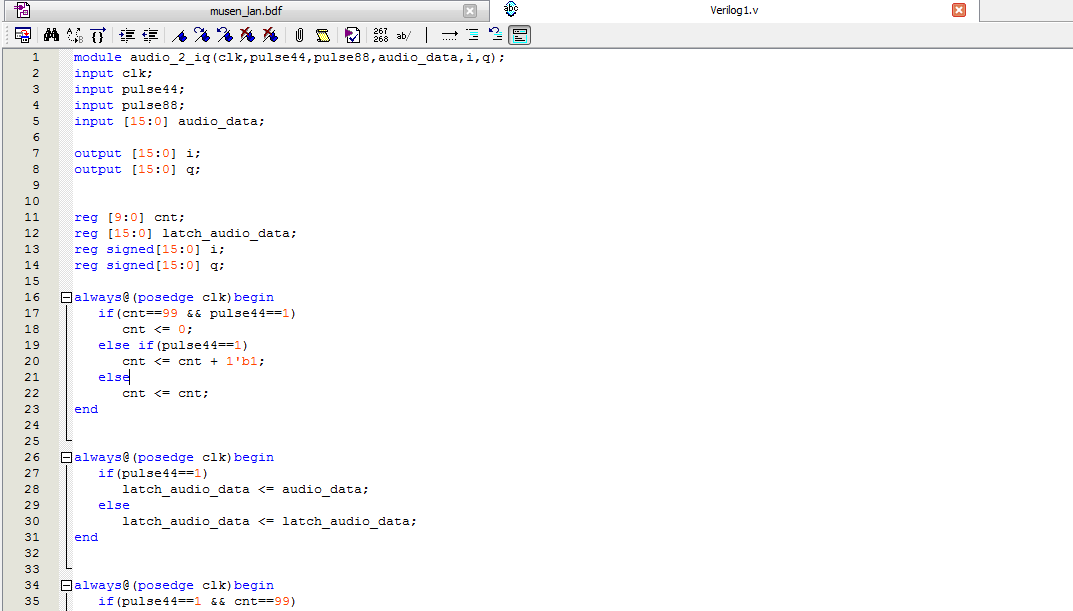

低速ADCから音声16ビットデータを受けてIQに変換するaudio_2_iqという名前のモジュールを作ります。

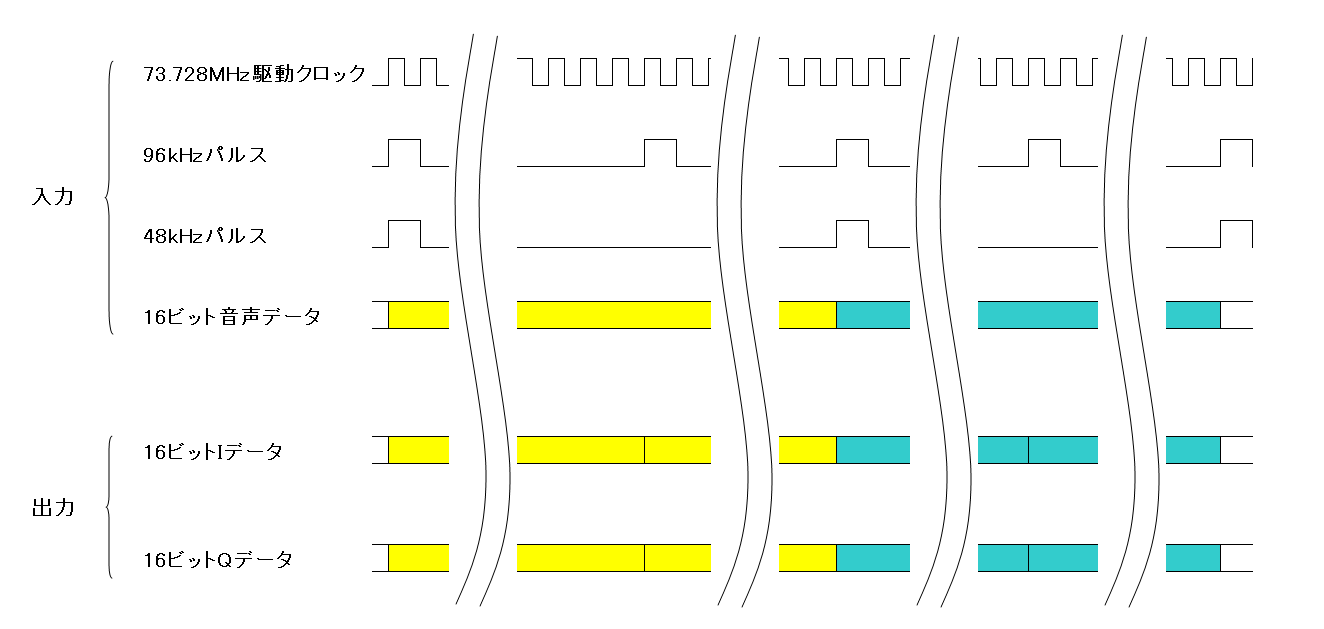

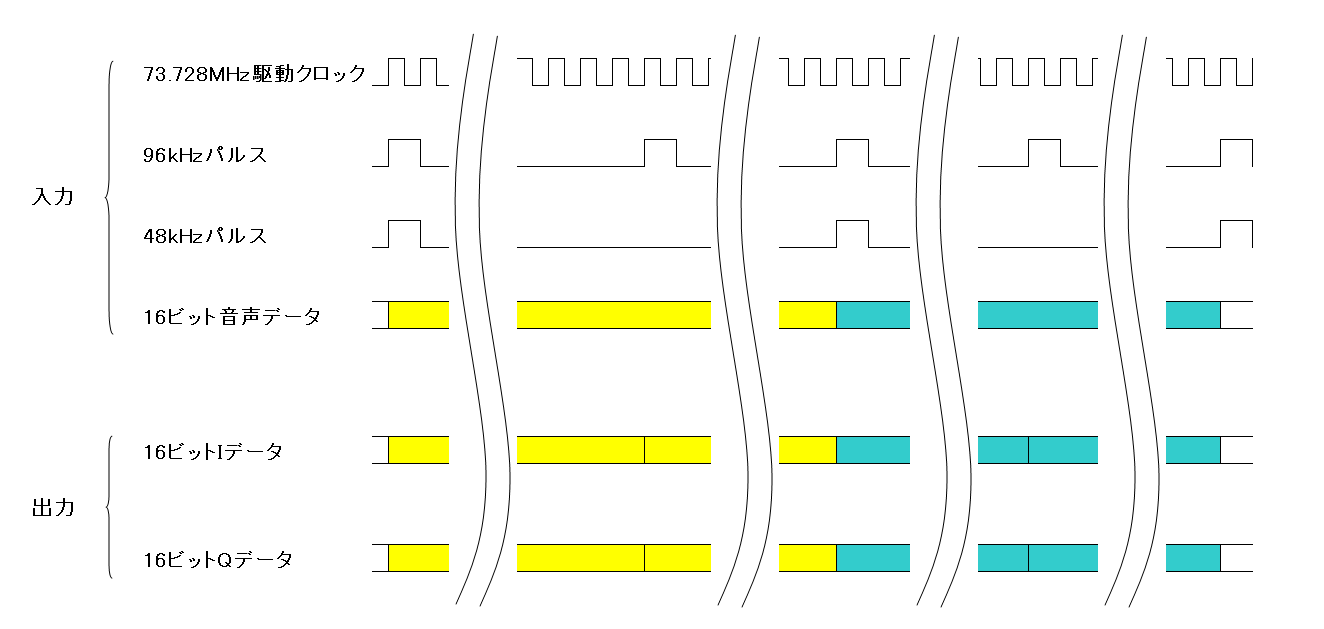

audio_2_iqのタイミングチャートは、下図のようにします。

外部から48kHzと96kHzのパルスをもらってきて、パルス毎にIQデータを更新していきます。

audio_2_iqモジュールを動作させるには、48kHzと96kHzのパルスが必要になります。

内部に100パルスをカウントする機能を持っていて、100回に1回特殊コードを出力するようにします。

特殊コードを出すタイミングは外部から制御しません。audio_2_iqは好き勝手なタイミングで(100回に1回という規則は守りながら)特殊コードを出力します。

※前までのページでは駆動周波数80MHzで音声のサンプルレートは44.1kHzとしていましたが使用する部品の都合で変更いたしました。

今後も仕様を変更する場合がありますので、ご了承ください。

audio_2_iqモジュールはVerilog-HDLというC言語によく似た言語で作成します。

コードは長くなりますので、別ファイルにしました。ダウンロードしてください。

※コードは今後のデバッグ作業で修正が入る可能性があることをご承知おきください。

ダウンロードしたコードをファームの中に組み込む作業をします。

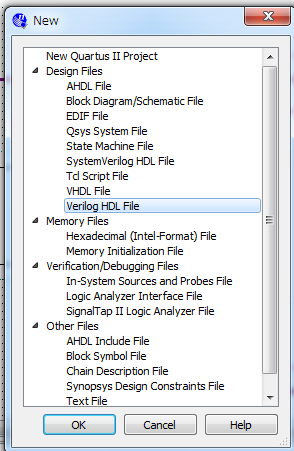

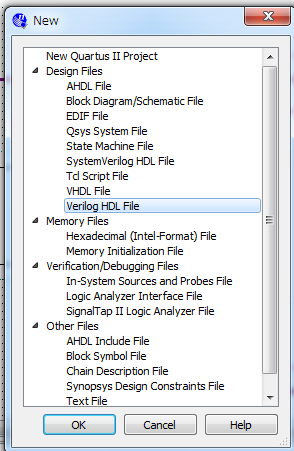

開発環境のメインメニューから File→New で新規ファイル一覧を開いて、Verilog HDL Fileを選びます。

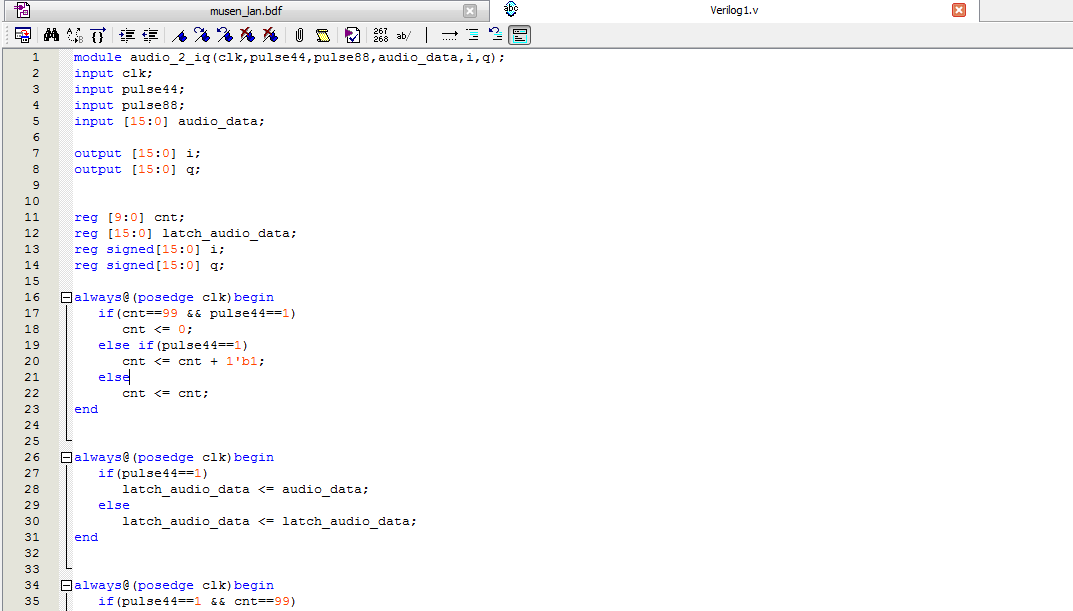

Verilogコードのテキストエディタが開きますからダウンロードしたコードをコピペしてください。

コードをコピペしましたら、Verilog1.v として保存します。

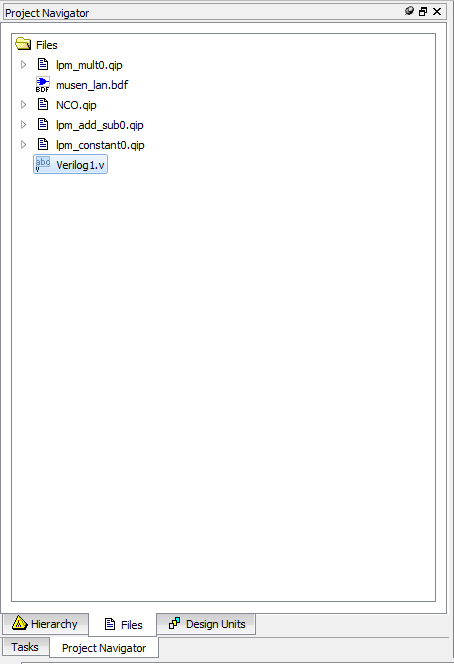

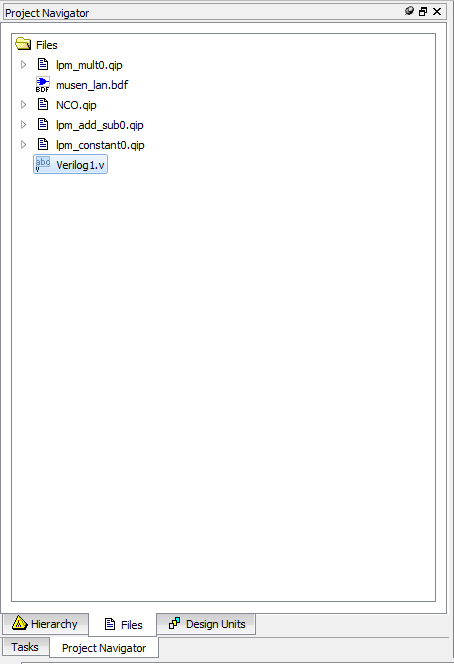

保存したコードを回路図に組み込みます。Project NavigatorのFilesタブを開くと、ソースファイルの一覧が出てきます。

先ほど保存したVerilog1.vを選んで右クリックして、Create Symbol File For Current Fileを実行します。

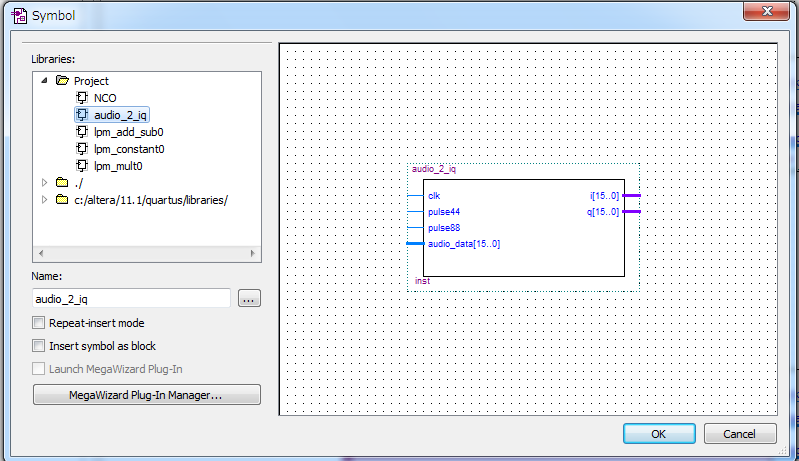

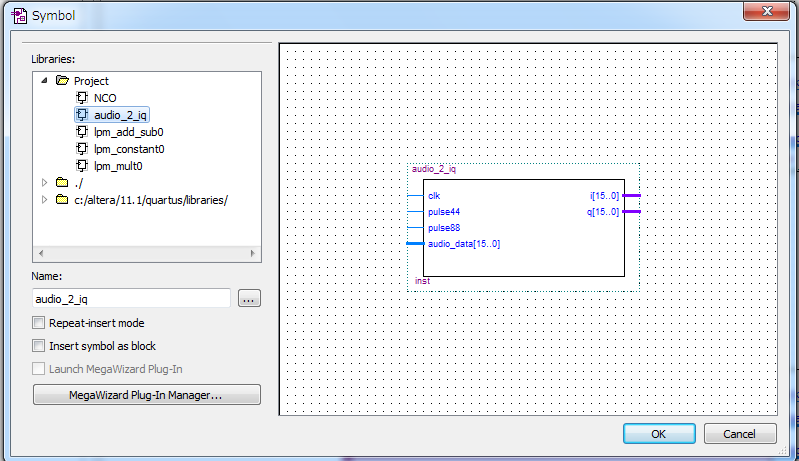

回路図(musen_lan.bsf)を開いて左ダブルクリックするとシンボル一覧を出すと、Verilog1.vに書いたaudio_2_iqというモジュールが、

シンボル化されています。audio_2_iqを選んで回路図に配置します。

2-送信FPGA-低速ADCのインターフェース回路

低速ADCとのインターフェースモジュールを作ります。

テキサスインスルツルメントのPCM4201というADコンバータを使用します。

PCM4201のデータシートはメーカサイトからダウンロードできます。

PCM4201は24ビット-96Ksps対応のADコンバータですが、今回は48kSpsで使用します。24ビットのデータうち下位の8ビットは捨てて実質16ビットのADCとして使用します。

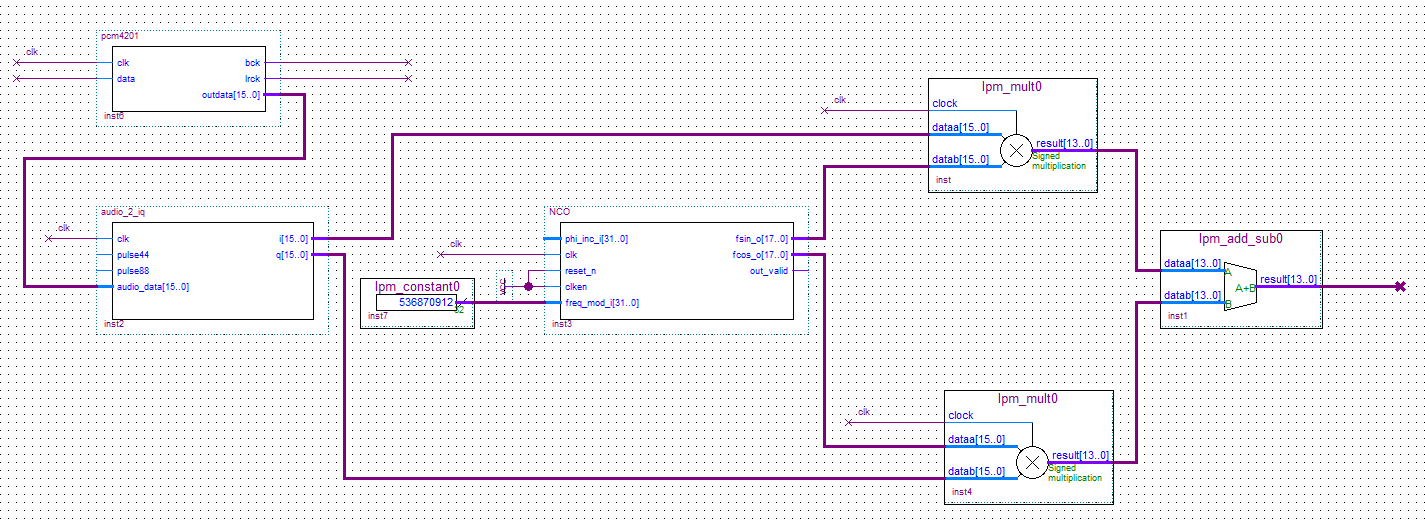

FPGA内部では音声16ビットデータは、16ビットパラレルデータ(16ビットバス)として扱われますが、PCM4201はシリアルインターフェスですから、

シリアルインターフェースで入力されたADCのデータをパラレルに変換するモジュールが必要になります。モジュールの名前はpcm4201にします。

pcm4201もVerilog-HDLで作ります。コードは長くなりますので、別ファイルにしました。ダウンロードしてください。

※コードは今後のデバッグ作業で修正が入る可能性があることをご承知おきください。

audio_2_iqの時と同じようにしてpcm4201をFPGAファームの中に組み込んでいきます。Verilog1.vにダウンロードしたpcm4201のコードを追記します。

ソースファイルの一覧からVerilog1.vを選んで右クリックして、Create Symbol File For Current Fileを実行します。

回路図(musen_lan.bsf)を開いて左ダブルクリックするとシンボル一覧にVerilog1.vに追記したpcm4201モジュールが、

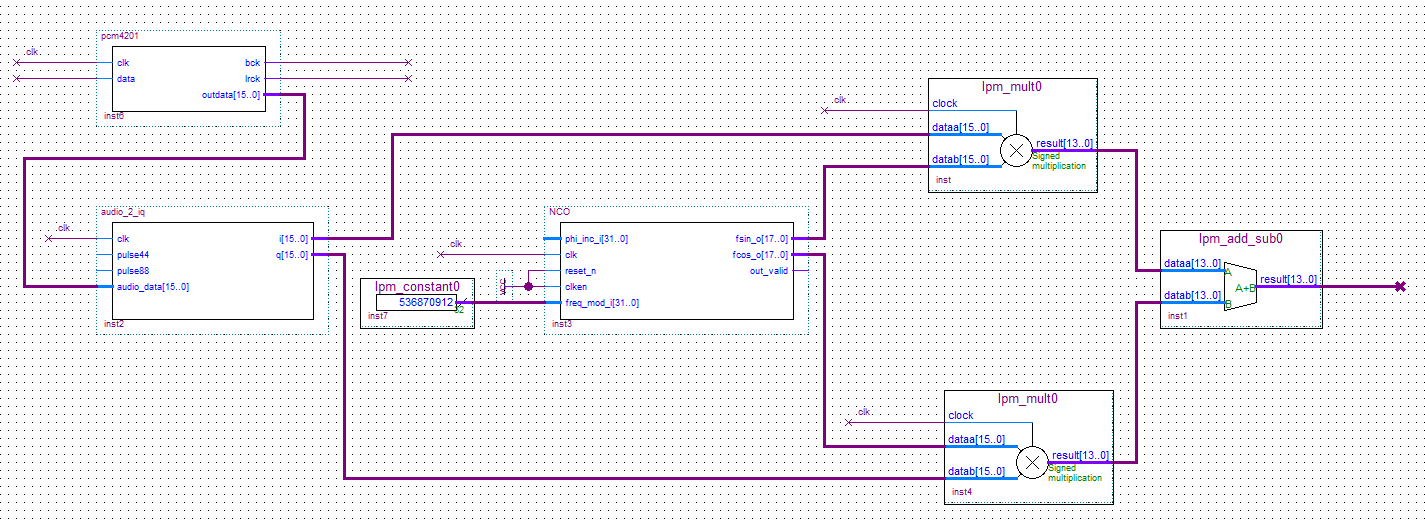

シンボル化されています。pcm4201を選んで回路図に配置します。最後にシンボル同士を結線します。

上の図はaudio_2_iqとpcm4201を回路図に追加して結線の終わった状態です。

次回も引き続き送信FPGAを作っていきます!

2015年1月12日 記

6ページ目に続く

戻る