オリジナルの無線LANをFPGAで作ろう 6ページ目

過去の記事はこちら 1ページ目 2ページ目 3ページ目

4ページ目 5ページ目

1-送信FPGA-パルス生成回路

5ページ目からのつづきです。FPGAのファームウェアを作っていきます。

前のページで作ったaudio_2_iqモジュールにパルスを与えるモジュールを作ります。

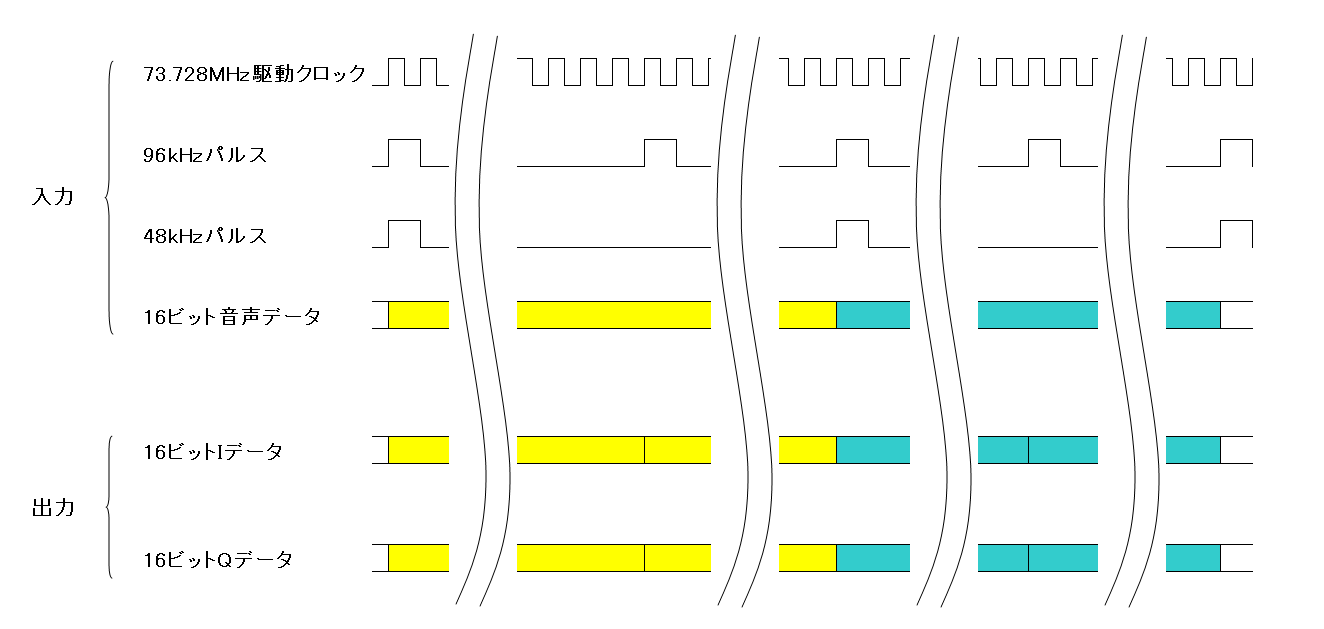

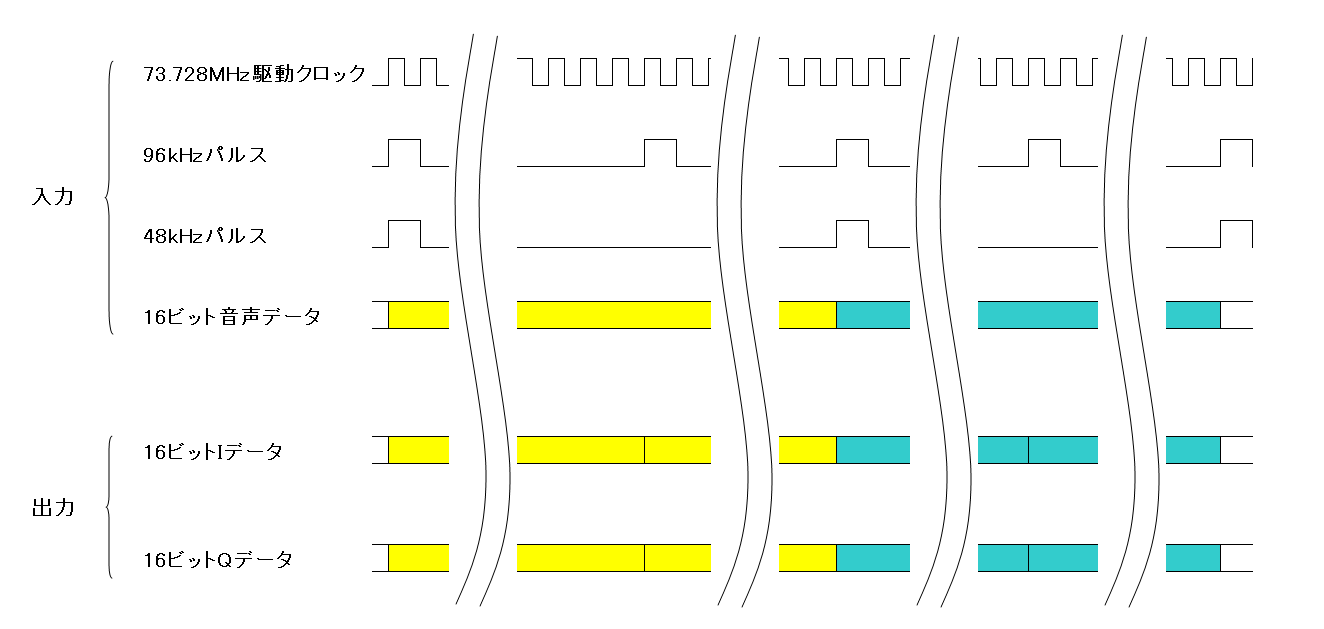

audio_2_iqモジュールに入力するパルスのタイミングの仕様は下図のとおりです。

96kHzパルスはFPGA駆動クロック73.728MHzの768分周です。48kHzパルスはFPGA駆動クロック73.728MHzの1536分周です。

パルスを与えるモジュールの名前はgen_pulseにします。gen_pulseモジュールはVerilogで作ります。

gen_pulseモジュールのソースコードはこちらからダウンロードしてください。

コードをダウンロードしましたらaudio_2_iqと同じようにしてコードを回路図に組み込みます。

回路図に組み込む手順の詳細は、5ページ目をご覧ください

2-送信FPGA-PLLモジュール

次にPLLモジュールを作ります。

FPGAに接続する水晶発振モジュールとして周波数24.576MHzのものを使用します。

FPGAの動作クロックは24.676MHzの3倍の73.728MHzとしていますから、入力した水晶の周波数を3逓倍するPLLが必要になります。

直接73.728MHzを入力せずに、PLLで3逓倍としたのは水晶の入手の都合です。

FPGAにはPLLが内蔵されていますから、希望の周波数の水晶がなくてもPLLを使うことで別の周波数の水晶で代替できます。

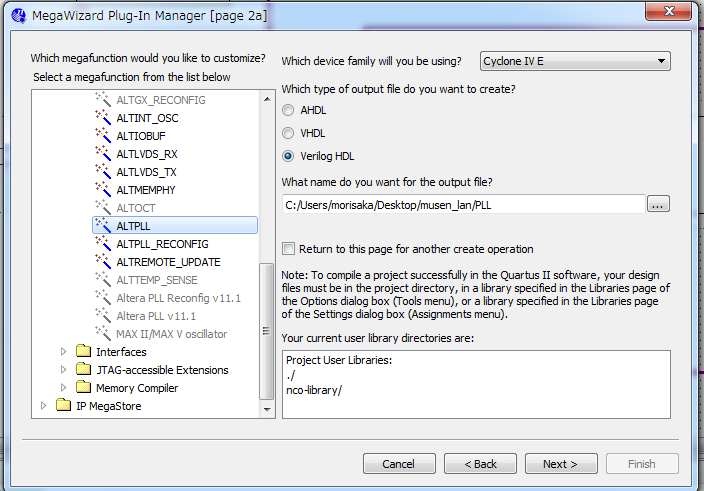

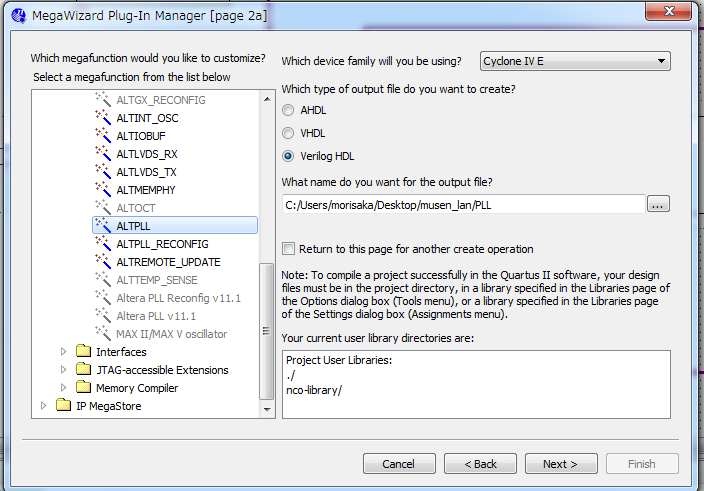

PLLモジュールは、メインメニュー → Tools → MegaWizard Plug-In Manager で作成します。

モジュール一覧からI/O→ALTPLLを選びます。名前はPLLにします。 NextをクリックするとPLLウィザードが出てきます。

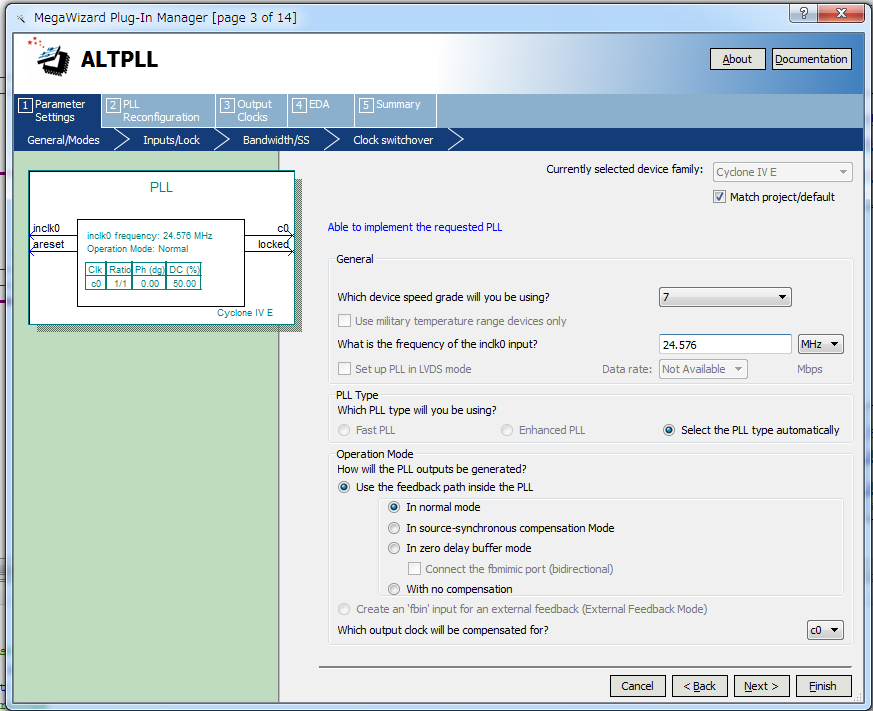

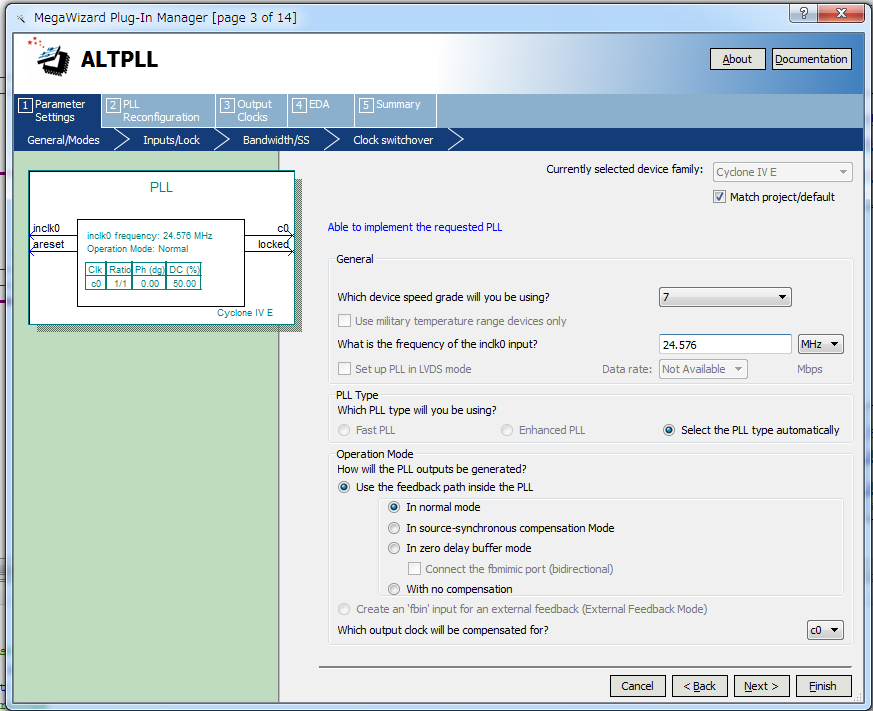

inck0の周波数に24.576MHzを設定して、Nextをクリックします。

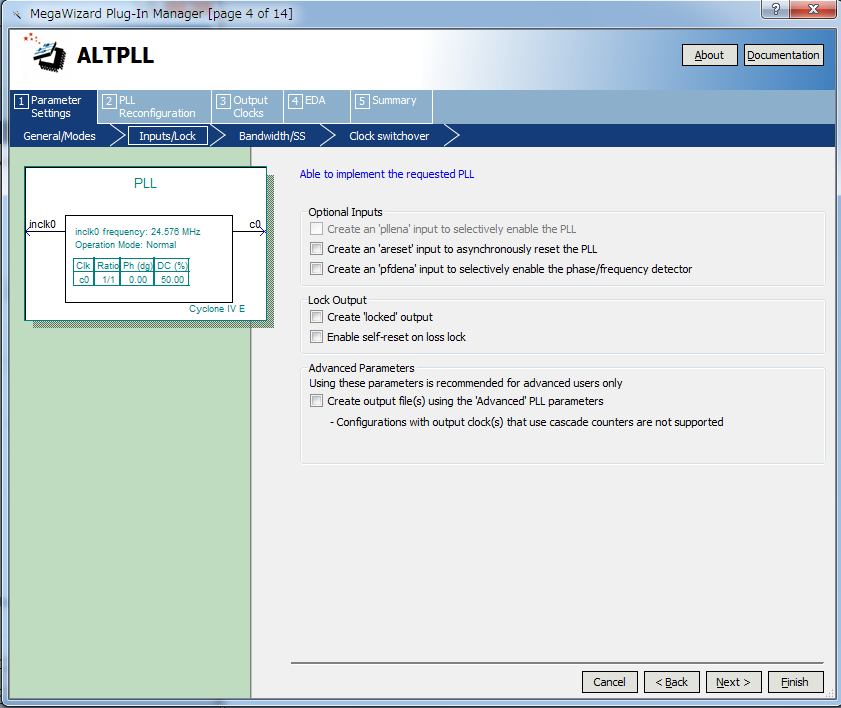

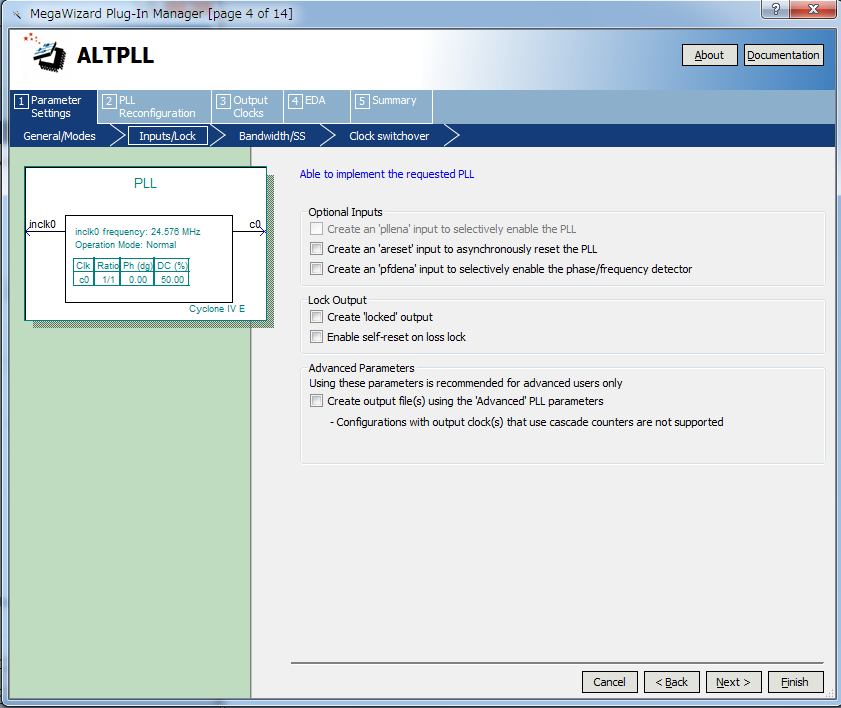

リセット端子(areset)などは必要ありませんので、すべてのチェックを外して、Nextをクリックします。

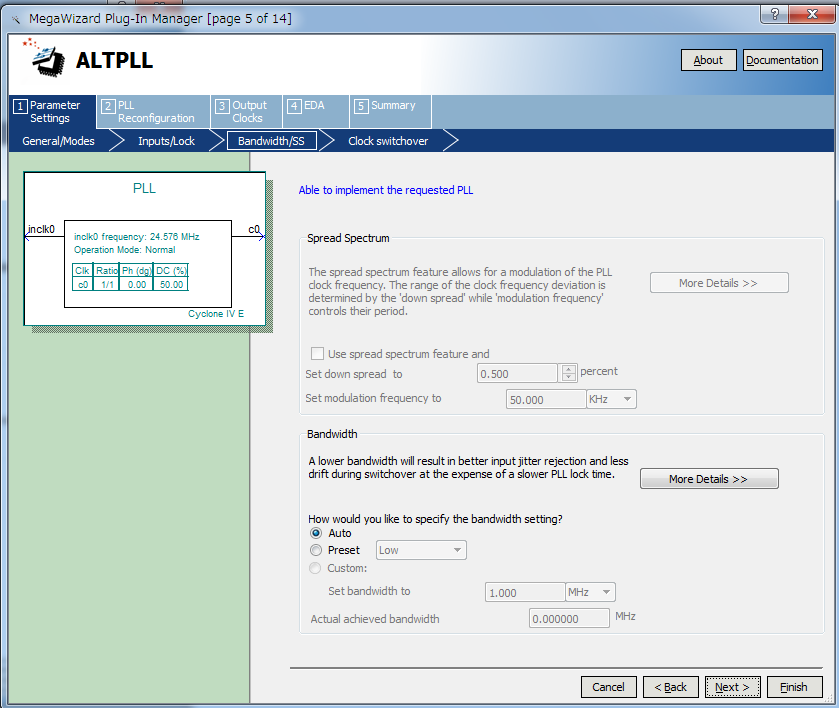

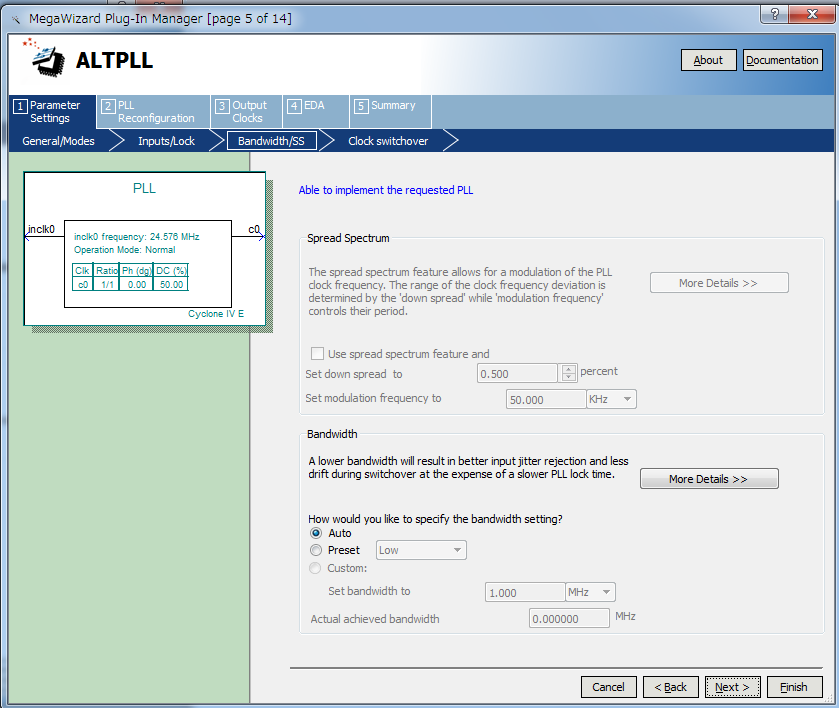

スペクトル拡散などは使いませんので、ここはすべてデフォルトの状態でNextをクリックします。

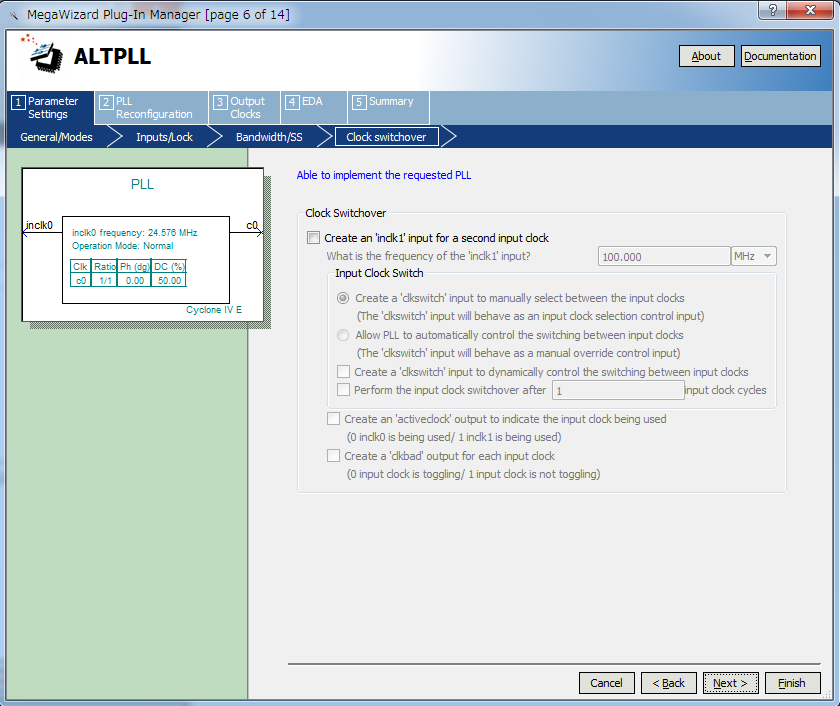

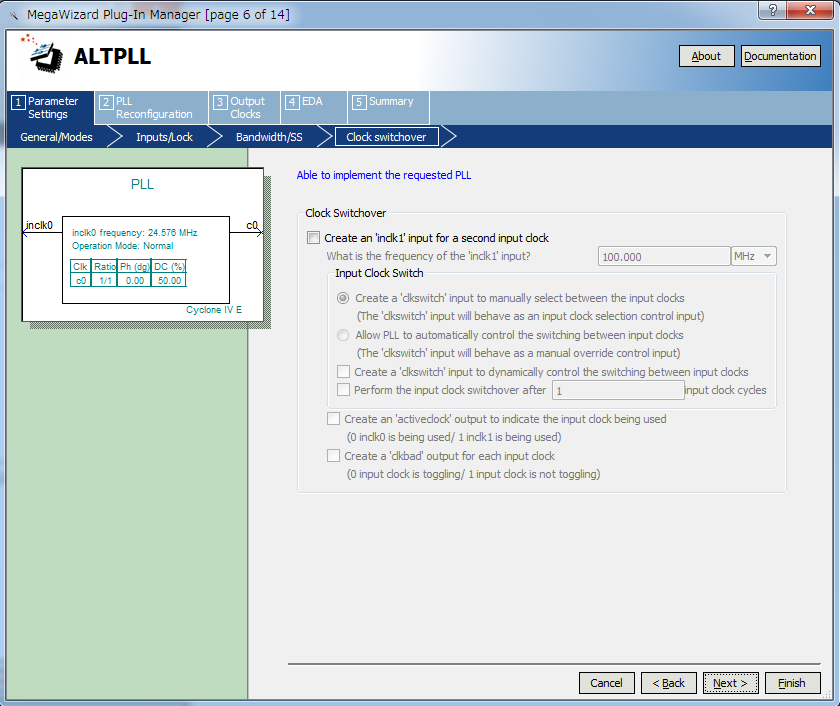

入力クロック切り替え機能は使いませんので、ここはすべてデフォルトの状態でNextをクリックします。

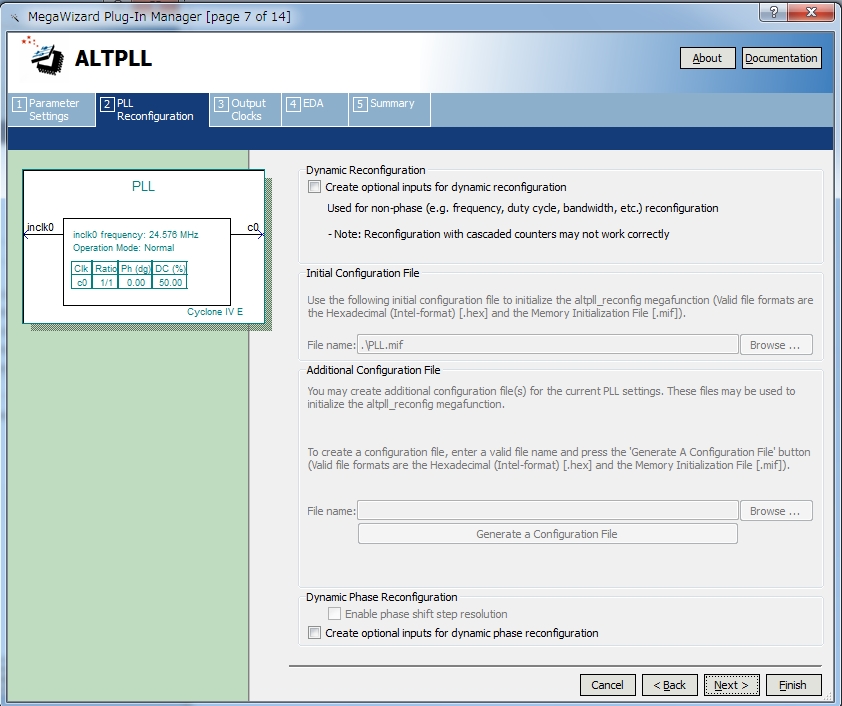

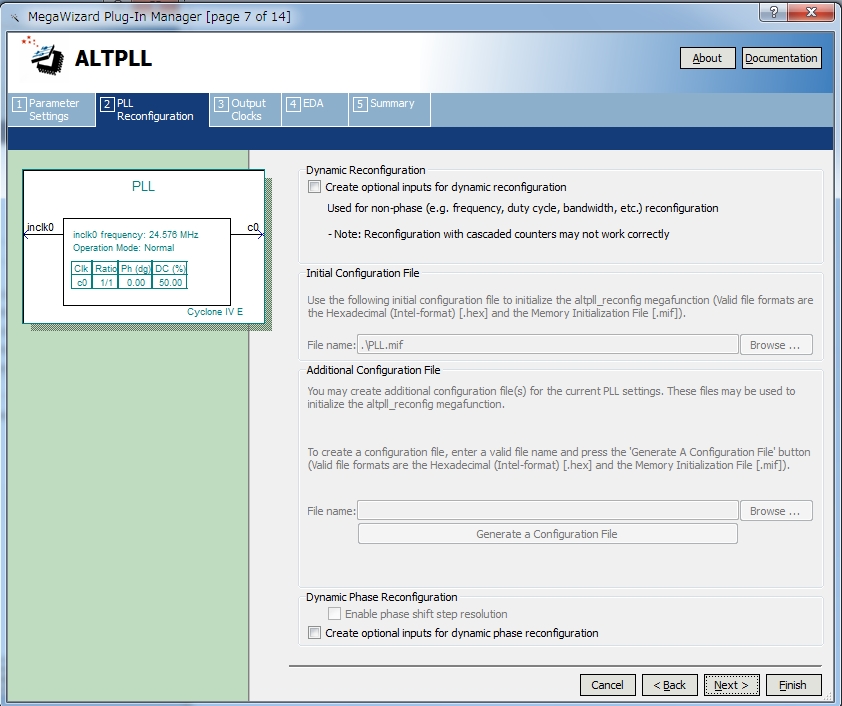

ダイナミックコンフィギュレーションは使いませんので、ここはすべてデフォルトの状態でNextをクリックします。

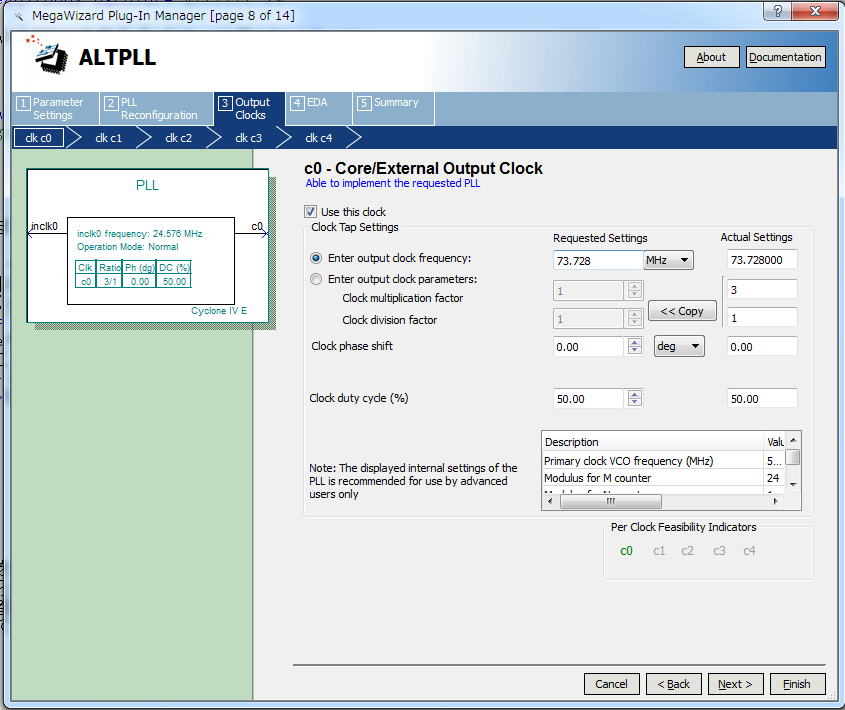

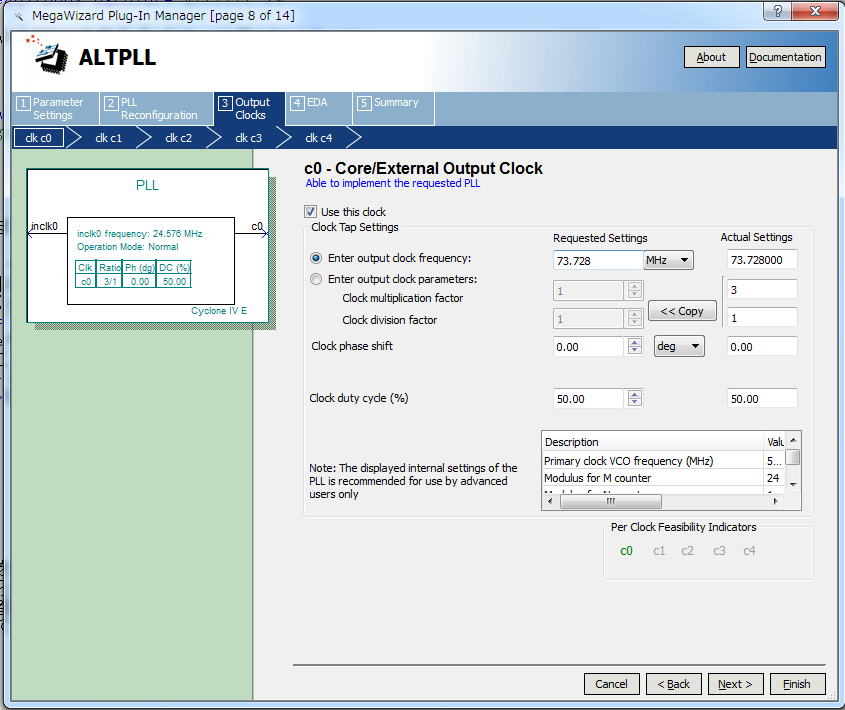

C0出力には73.728MHzを設定すると逓倍数が"3"と自動計算されます。Nextをクリックします。

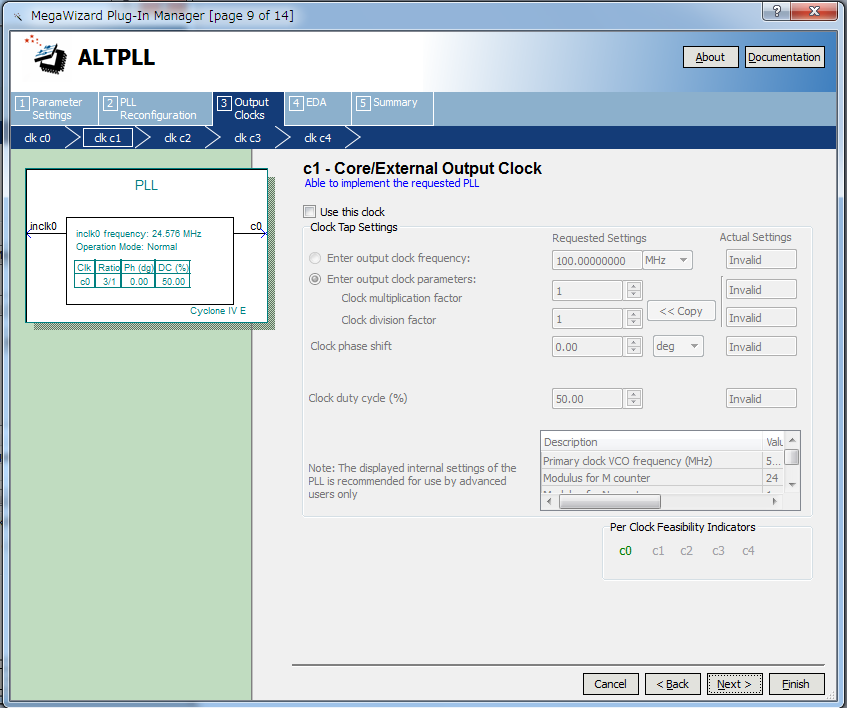

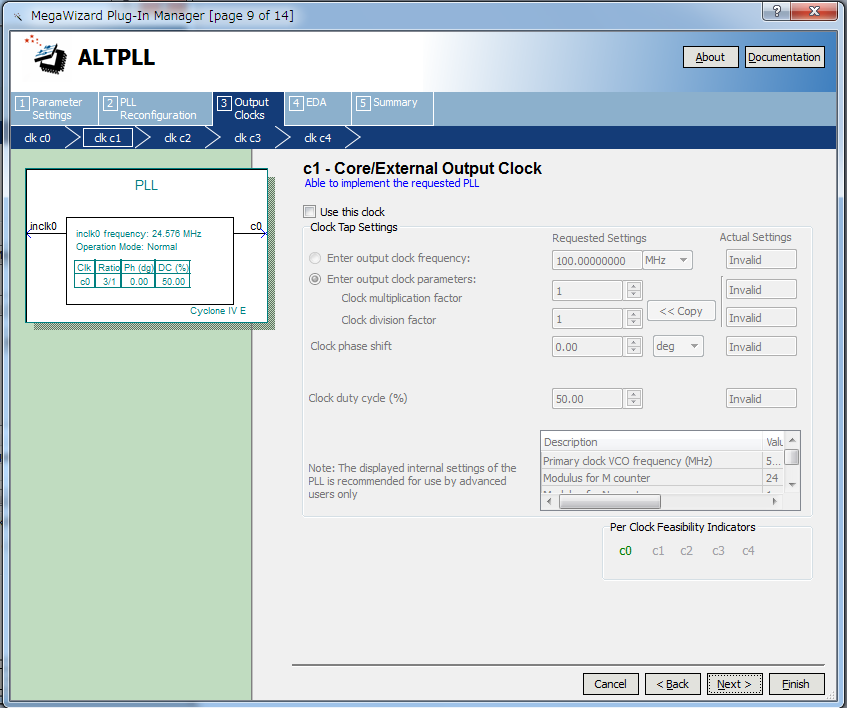

C1出力は使いません。FPGA内部で複数のクロックを使う場合はC1出力を使います。ここはデフォルトのままでNextをクリックします。

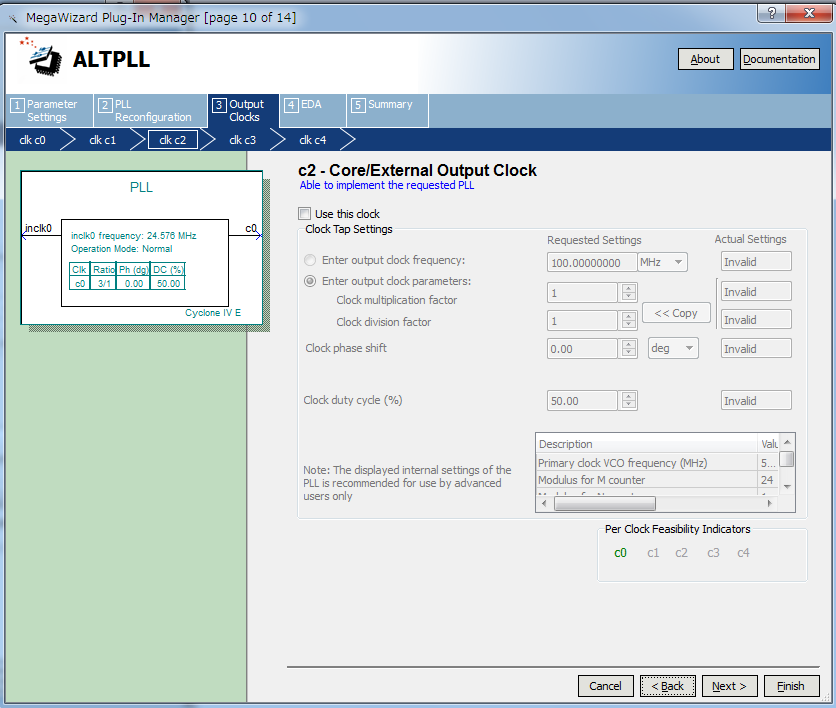

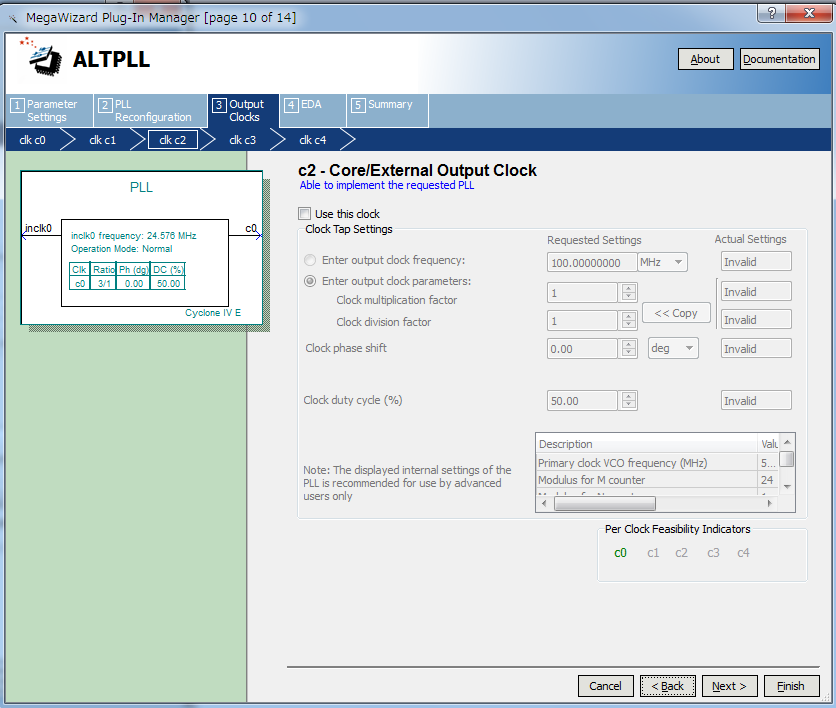

C2出力は使いませんので、ここはデフォルトのままでNextをクリックします。

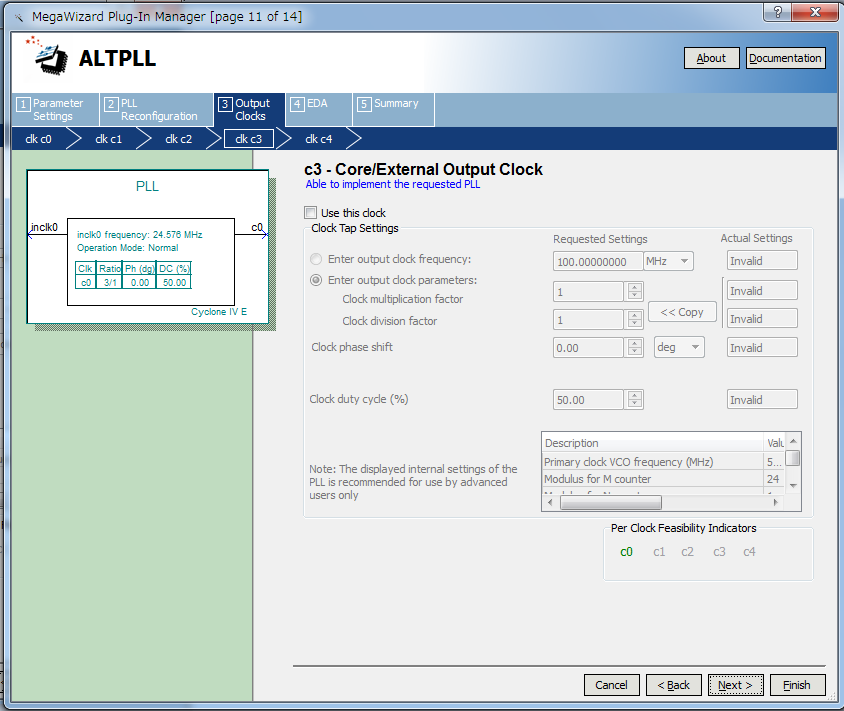

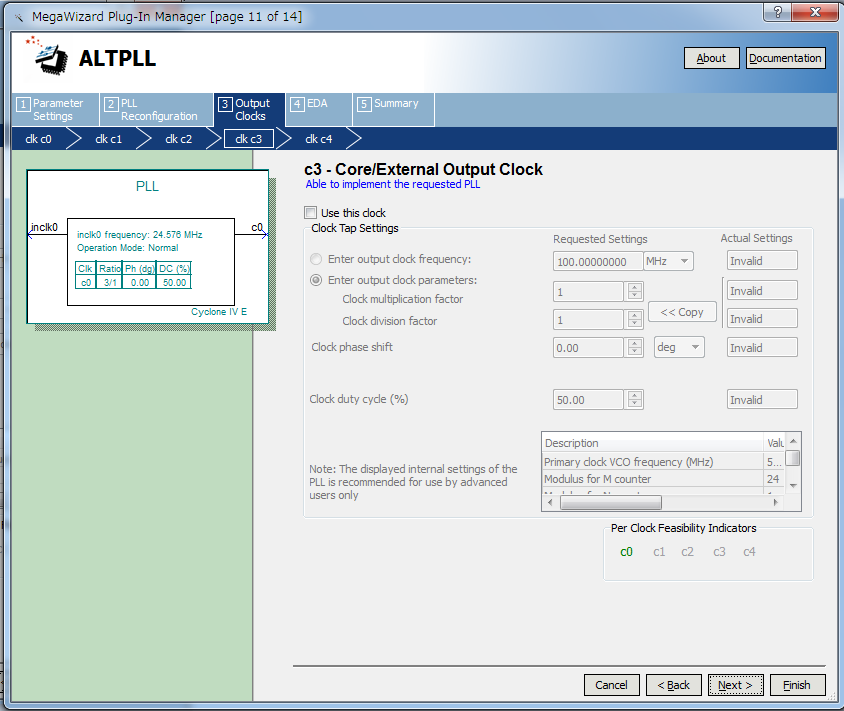

C3出力は使いませんので、ここはデフォルトのままでNextをクリックします。

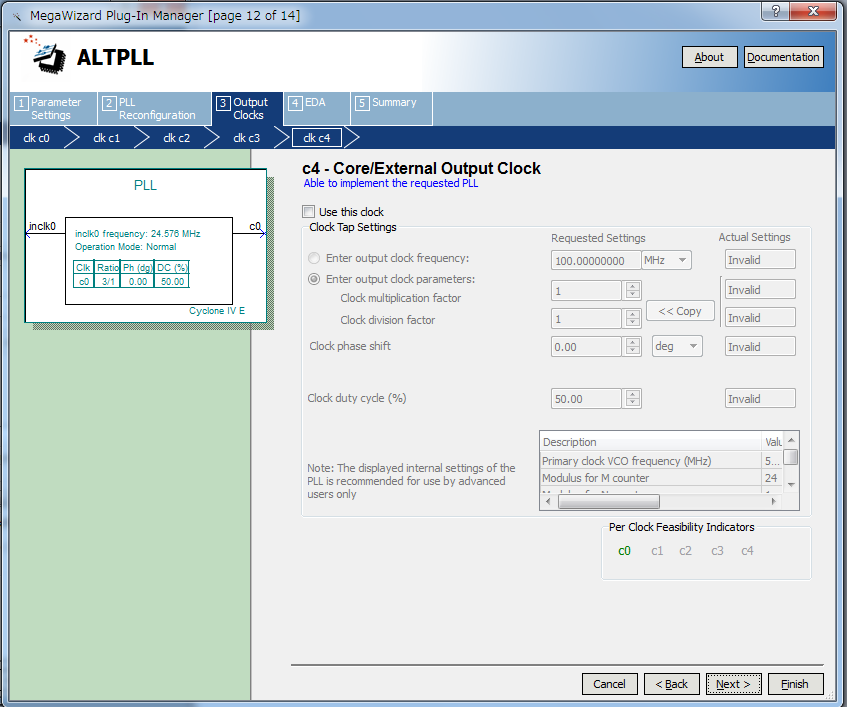

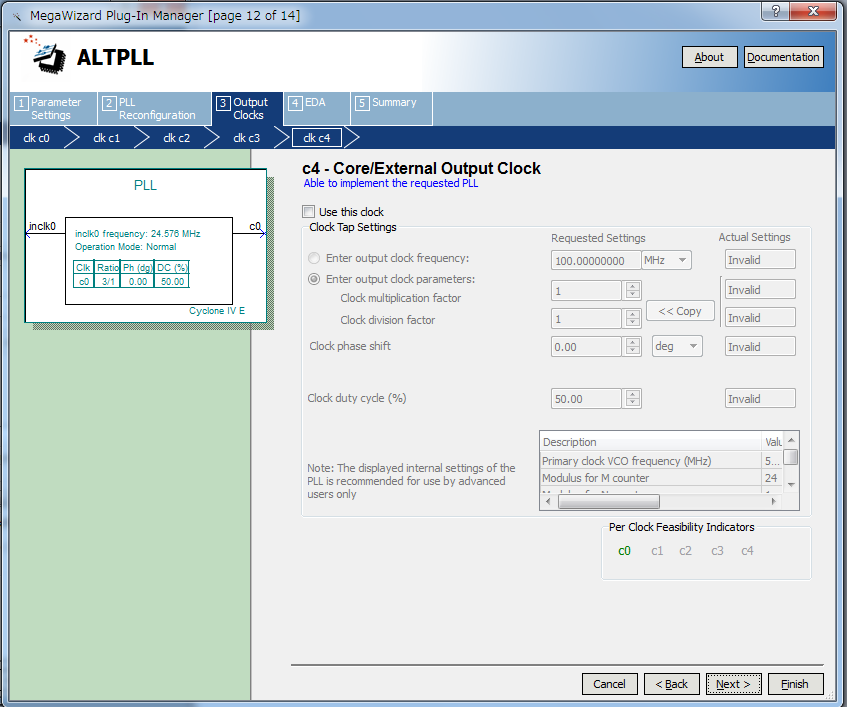

C4出力は使いませんので、ここはデフォルトのままでNextをクリックします。

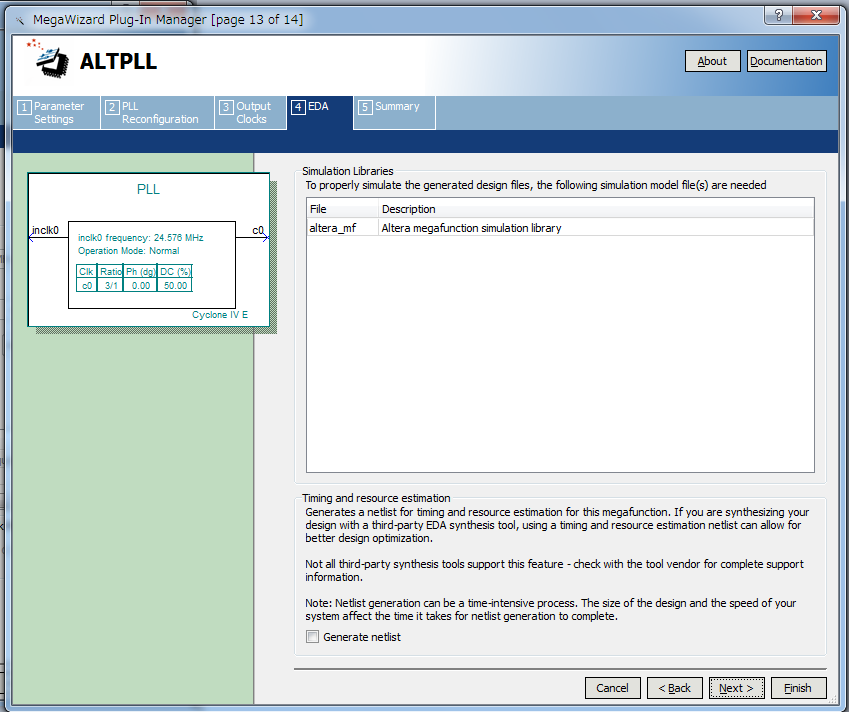

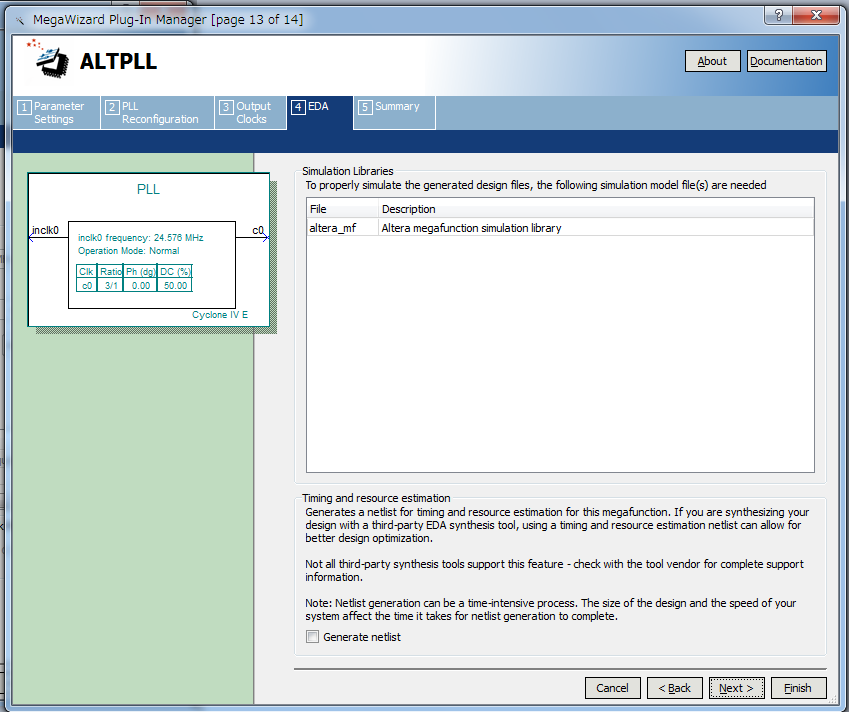

シミュレーション設定はデフォルトのままでNextをクリックします。

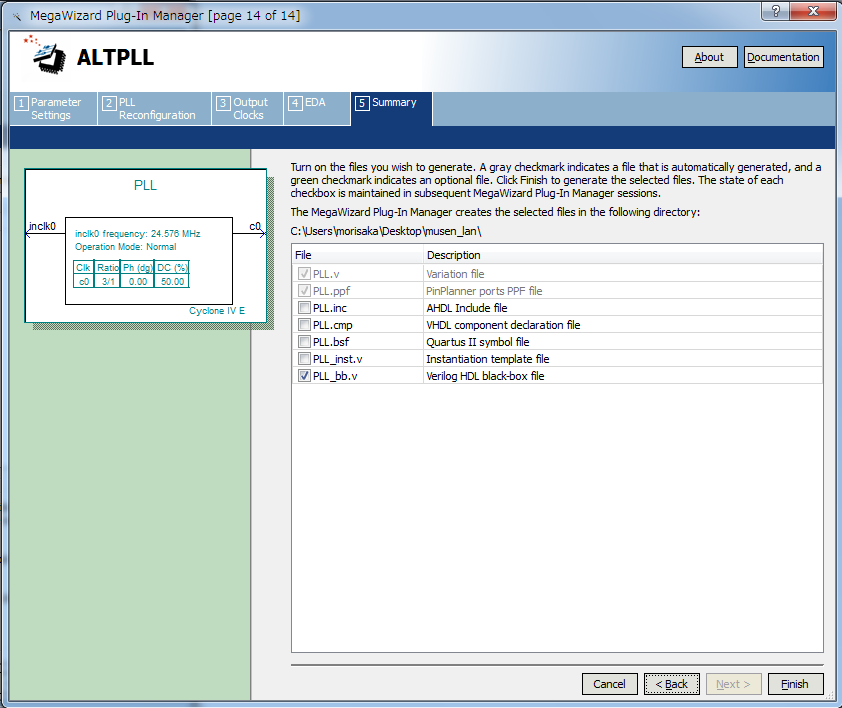

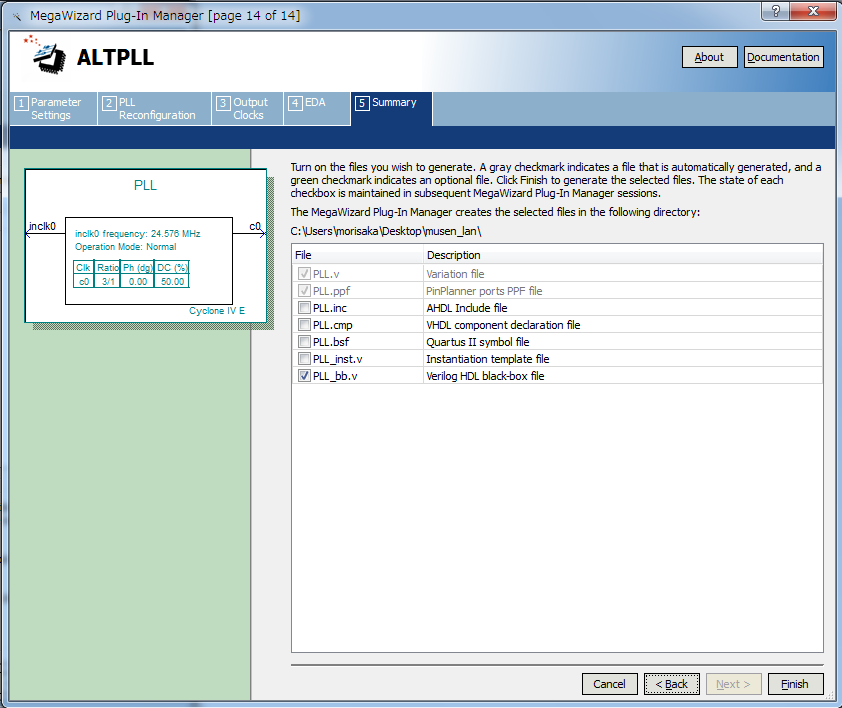

サマリーはデフォルトのままでFinishをクリックします。

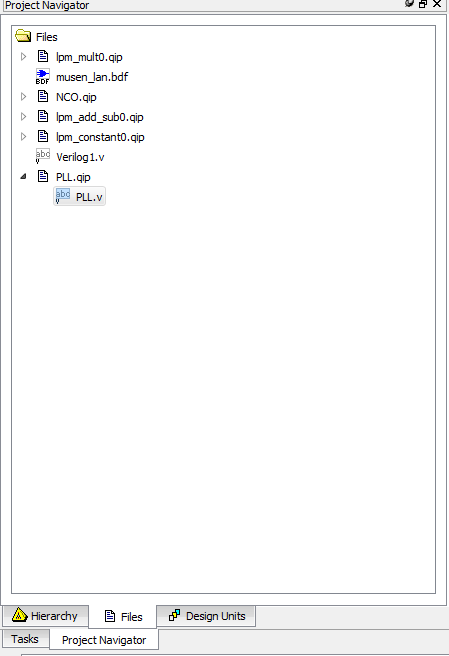

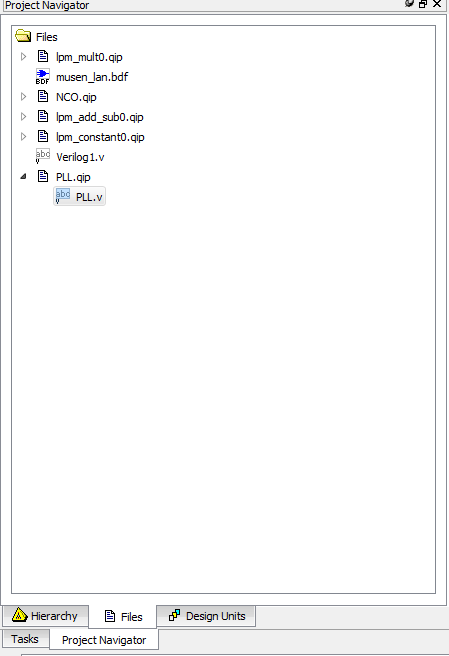

PLLを回路図に組み込むにはもう一つ作業があります。ソース一覧にPLL.vというVerilogファイルが追加されています。

PLL.vを選んで右クリックして、Create Symbol File For Current Fileを実行します。

回路図(musen_lan.bsf)を開いて左ダブルクリックするとシンボル一覧を出すとPLLモジュールがシンボル化されていますから、

回路図に配置します。

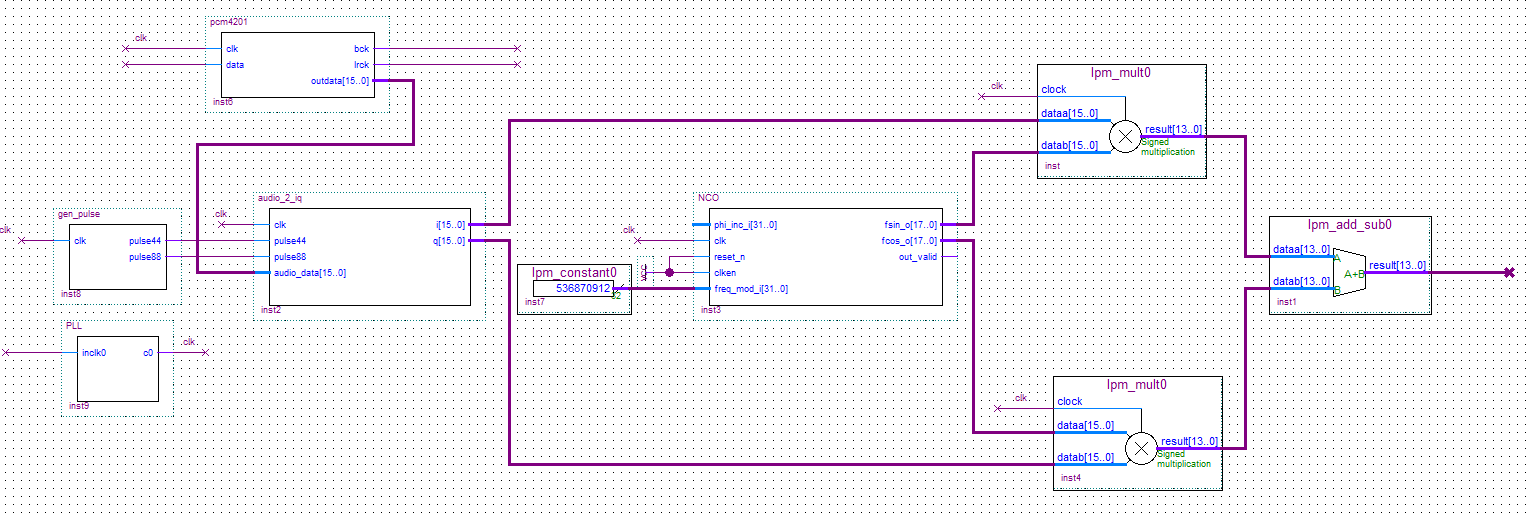

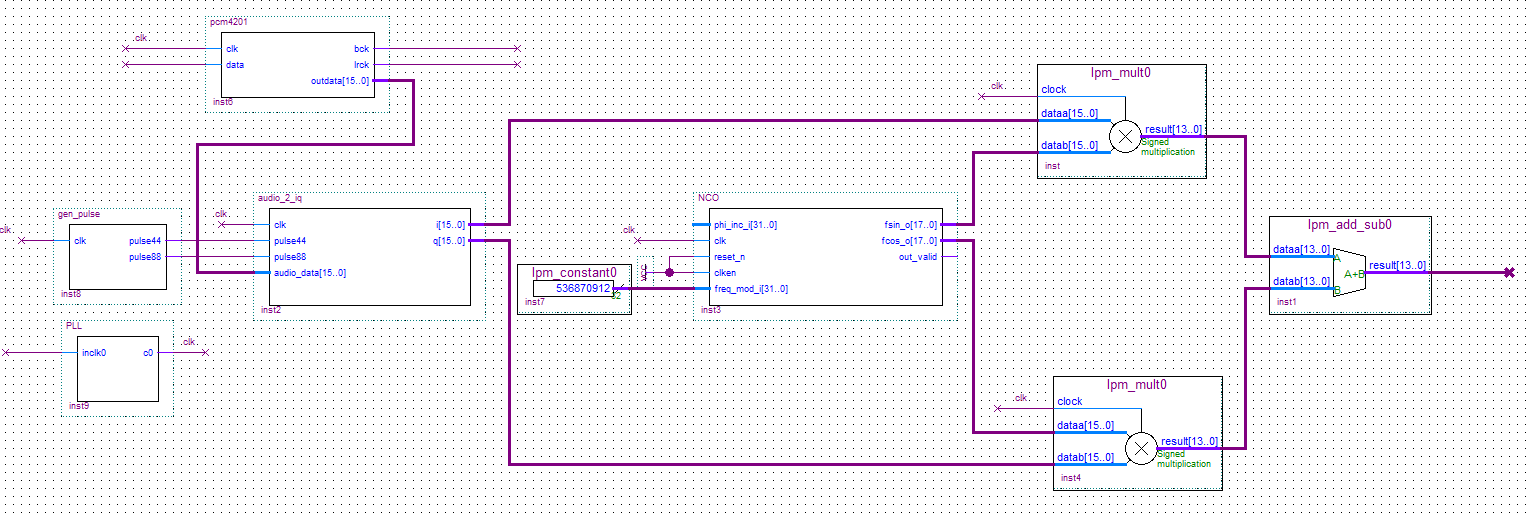

gen_pulseモジュールと、PLLを追加して、モジュール同士を結線します。

上の図は結線の終わった回路図です。

次回も引き続き送信FPGAを作っていきます!

2015年1月16日 記

7ページ目に続く

戻る