オリジナルの無線LANをFPGAで作ろう 19ページ目

過去の記事はこちら

1ページ目 2ページ目 3ページ目

4ページ目 5ページ目

6ページ目 7ページ目 8ページ目 9ページ目 10ページ目

11ページ目 12ページ目 13ページ目 14ページ目

15ページ目 16ページ目 17ページ目 18ページ目

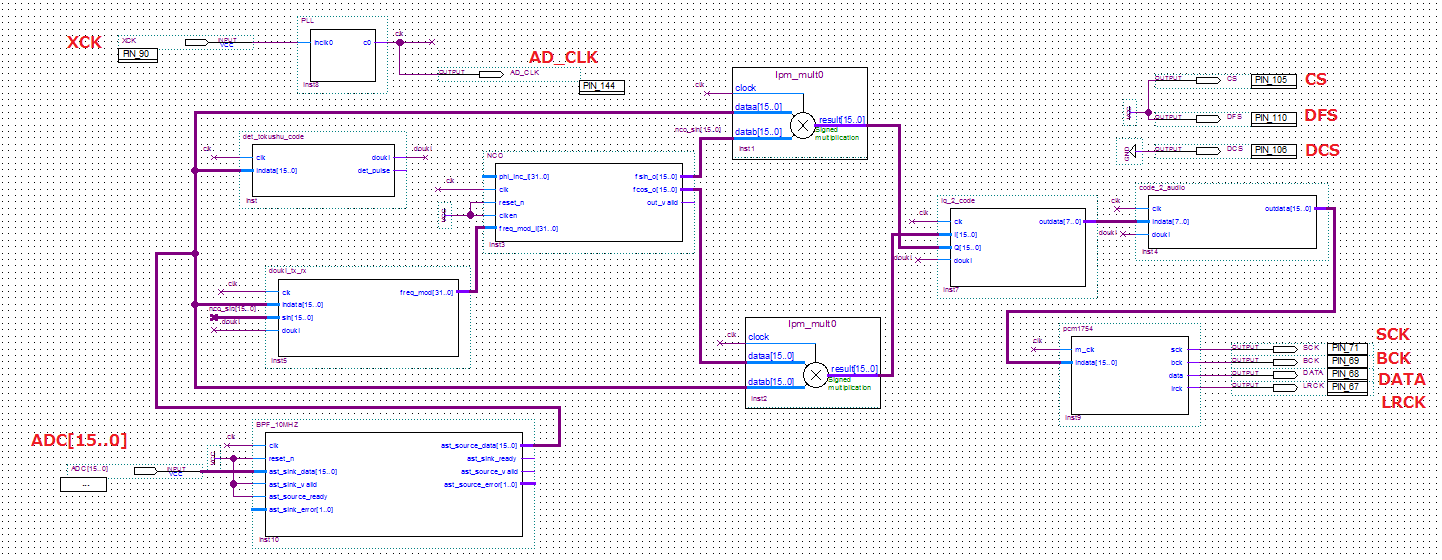

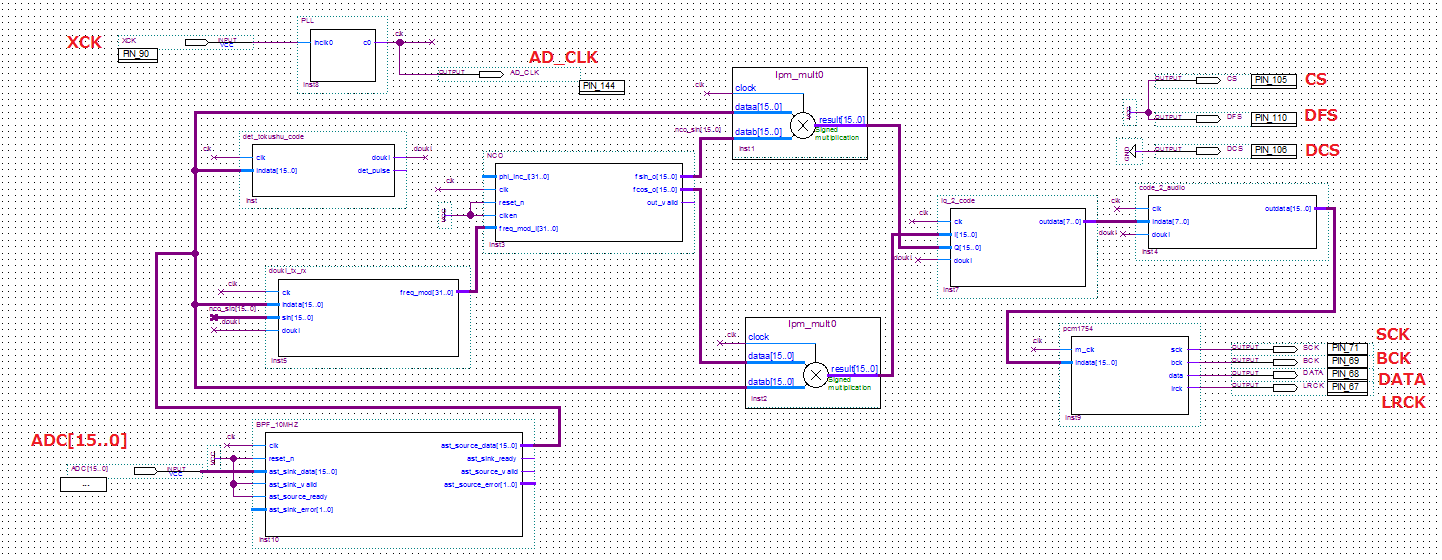

1-受信FPGAのファーム作成-入出力ピンを設ける

送信側のデバッグで途切れていた受信ファームの作成の続きを進めていきます。

受信側ファームは14ページ目でほぼ完成していました。14ページ目の状態に入出力ピンを配置します。

入力ピン:XCK,ADC[15..0],

出力ピン:AD_CLK,SCK,BCK,DATA,LRCK,CS,DFS,DCS

を回路図に配置してください。

なお、入出力ピンを配置する手順は、7ページ目をご覧下さい。

出力ピン:CS,DFS,DCSはADCのモード設定ピンです。CS,DFSにVCCを、DCSにGNDを繋ぐと、ADCは2の補数、CMOSパラレル出力モードで動作します。

ADCはADC1610を使います。モード設定については、メーカサイトからダウンロードできるデータシートに記載されています。

入出力ピンの配置が終わったら、コンパイルを実行して、コンパイルが通ることを確認します。

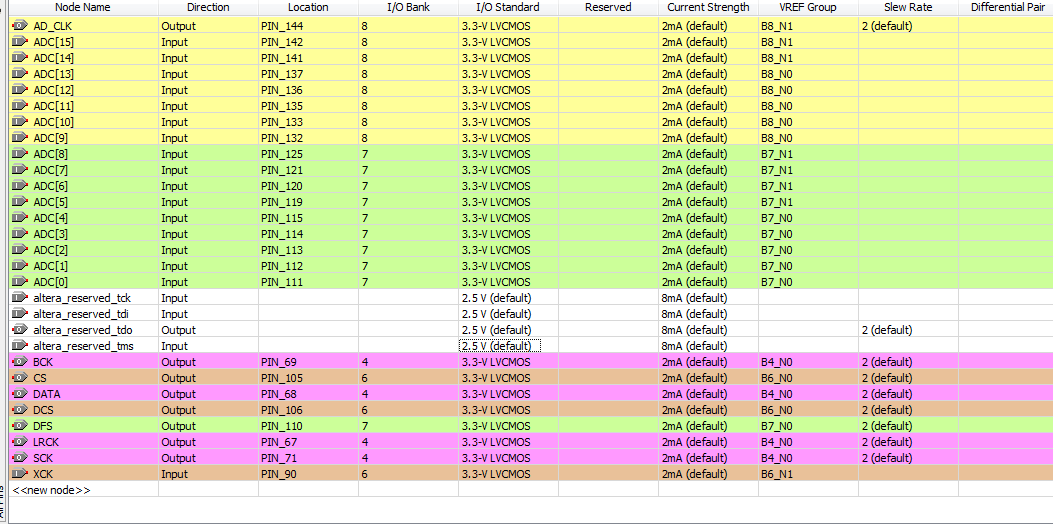

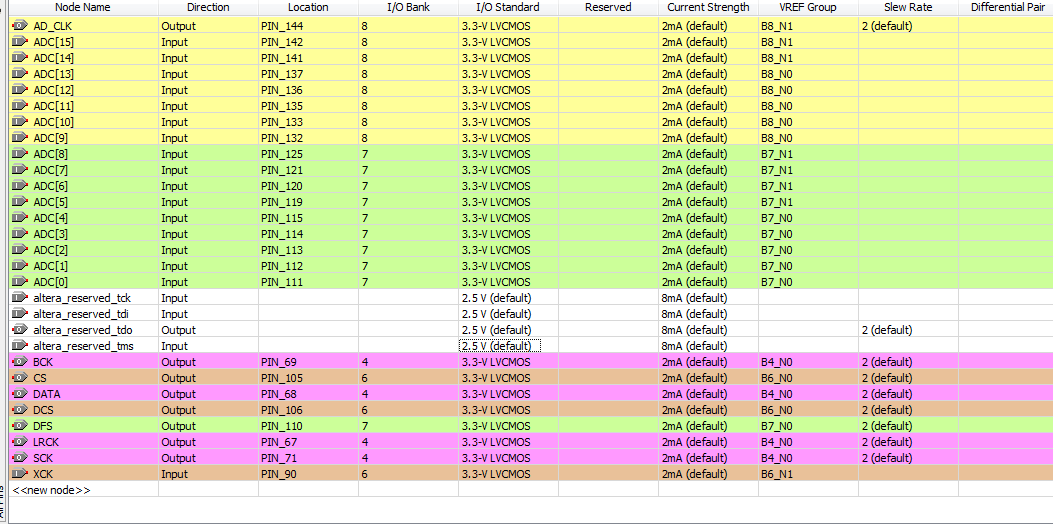

2-受信FPGAのファーム作成-入出力ピンのピン番号アサイン

受信側のFPGAを含めた全体の回路図をこちらからダウンロードしてください。

メインのFPGAの他に10MHz帯の信号を取り込む高速ADコンバータ、オーディオ信号を出力する低速DAコンバータで構成されています。

その他に各部に電源を供給する電源部があります。

回路図に沿ってピン番号を入力していきます。ピン番号の入力の手順は、9ページ目をご覧下さい。

altera*以外のピンのI/O standardを3.3V-CMOSに変更することも忘れずしておいてください。

ピン番号の入力が終わったら、もう一度コンパイルしてコンパイルが通ることを確認してください。

2015年3月24日 記

20ページ目に続く

戻る