オリジナルの無線LANをFPGAで作ろう 18ページ目

過去の記事はこちら

1ページ目 2ページ目 3ページ目

4ページ目 5ページ目

6ページ目 7ページ目 8ページ目 9ページ目 10ページ目

11ページ目 12ページ目 13ページ目 14ページ目

15ページ目 16ページ目 17ページ目

1-送信側の基板で実機デバッグ

送信側のデバッグをやっていきます。シグナルタップを使ったりしながら、送信側ファームの検証をしたところ、

3箇所の修正するべき箇所が見つかりました。

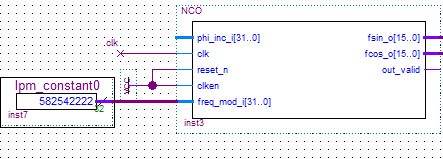

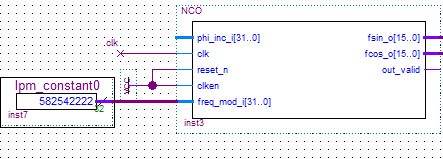

1.NCOの設定周波数

途中でFPGAの駆動周波数を80MHz→73.728MHzに変更したので、NCOの周波数設定値を変更する必要があったのですが、変更を忘れていました。

NCOの周波数端子に接続されている定数モジュール(lpm_const0)をダブルクリックして、0x20000000 → 0x22B8E38E に変更してくだい。

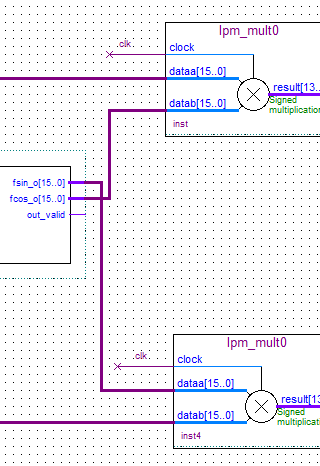

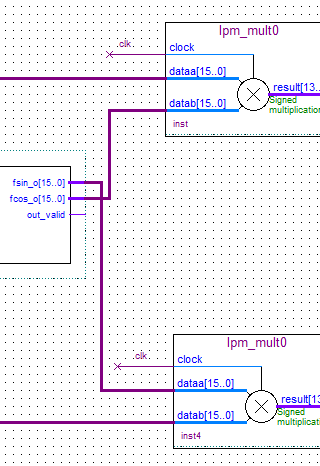

2.NCOのサイン・コサイン出力を入れ替え

IQ変調器では、NCOのサイン出力、コサイン出力の両方を使いますが、サイン・コサインが逆になっていました。

サイン・コサインを入れ替える修正をしてください。

3.audio_2_iqモジュールの修正

audio_2_iqのVerilogコードに間違いがありました。修正済Verilogコードをこちらからダウンロード

していただいて、差し替えをお願いします。

受信側と接続してみると新たなバグが発見される可能性はありますが、ひとまず送信側ファームははこれで完成です。

次回は、一旦途切れていた受信側ファームウェアの作成に戻ります。

2015年3月18日 記

19ページ目に続く

戻る