僆儕僕僫儖偺柍慄LAN傪FPGA偱嶌傠偆 17儁乕僕栚

夁嫀偺婰帠偼偙偪傜

1儁乕僕栚 2儁乕僕栚 3儁乕僕栚

4儁乕僕栚丂5儁乕僕栚

丂6儁乕僕栚丂7儁乕僕栚丂8儁乕僕栚丂9儁乕僕栚丂10儁乕僕栚

丂11儁乕僕栚丂12儁乕僕栚丂13儁乕僕栚丂14儁乕僕栚

丂15儁乕僕栚丂16儁乕僕栚

1-憲怣懁偺婎斅偱幚婡僨僶僢僌

憲怣懁偺僨僶僢僌傪傗偭偰偄偒傑偡丅崱夞偼僨僶僢僌僣乕儖偺僔僌僫儖僞僢僾偺巊偄曽傪愢柧偟傑偡丅

僔僌僫儖僞僢僾偼FPGA撪晹丒僺儞偺怣崋傪儌僯僞偱偒傞僣乕儖偱偡丅僺儞偵弌偝側偔偰傕丄FPGA撪晹偺怣崋偑尒偊傞偺偱僨僶僢僌偵偲偰傕曋棙偱偡丅

傑偨丄僶僗傪傑偲傔偰悢抣壔偟偨傝僌儔僼壔偟偨傝丄崅婡擻偺儘僕僢僋傾僫儔僀僓偺傛偆側巊偄曽偑偱偒傑偡丅

僔僌僫儖僞僢僾偺尨棟傪娙扨偵愢柧偟傑偡丅

僔僌僫儖僞僢僾偼僩儕僈偑擖傞偲儌僯僞懳徾偺FPGA撪晹丒僺儞偺怣崋傪FPGA撪晹偺SRAM偵拁偊偼偠傔傑偡丅僔僌僫儖僞僢僾偱偼儌僯僞挿傪偁傜偐偠傔愝掕偟偰偍偒傑偡偑丄

愝掕偝傟偨儌僯僞挿偵側傞傑偱SRAM偵怣崋傪拁偊懕偗傑偡丅愝掕偝傟偨挿偝偵払偡傞偲丄JTAG僺儞仺FPGA彂偒崬傒婍仺PC偵僨乕僞傪揮憲偟傑偡丅偦偟偰PC偱丄僨乕僞傪昞帵偟傑偡丅

FPGA撪晹偺SRAM偵儌僯僞怣崋傪堦扷拁偊傞尨棟偱偡偺偱丄USB揮憲偱偼懷堟晄懌偵側傞傛偆側懡價僢僩丒挻崅懍偺怣崋傕儌僯僞偡傞偙偲偑偱偒傑偡丅

儌僯僞偟偨偄怣崋偲FPGA撪晹偺SRAM傪愙懕偡傞昁梫偑偁傝傑偡偺偱丄栚揑偺怣崋偺儌僯僞偑弌棃傞傛偆偵偡傞偨傔偵嵞僐儞僷僀儖偑昁梫偱偡丅

FPGA撪晹偵丄儌僯僞偡傞怣崋偺價僢僩暆亊儌僯僞挿偺SRAM偺嬻偒偑昁梫偱偡丅

掅懍ADC偱庢傝崬傫偩16價僢僩偺壒惡怣崋偺儌僯僞傪椺偵僔僌僫儖僞僢僾偺巊偄曽傪愢柧偟傑偡丅

傑偢僔僌僫儖僞僢僾傪棫偪忋偘傑偡丅儊僀儞儊僯儏乕丂仺丂Tools丂仺丂SignalTap嘦LogicAnalizer偵偰僔僌僫儖僞僢僾偑棫偪忋偑傝傑偡丅

僔僌僫儖僞僢僾偱愝掕偡傞崁栚偼丄儌僯僞挿偲丄僋儘僢僋偲丄儌僯僞懳徾偺怣崋偱偡丅

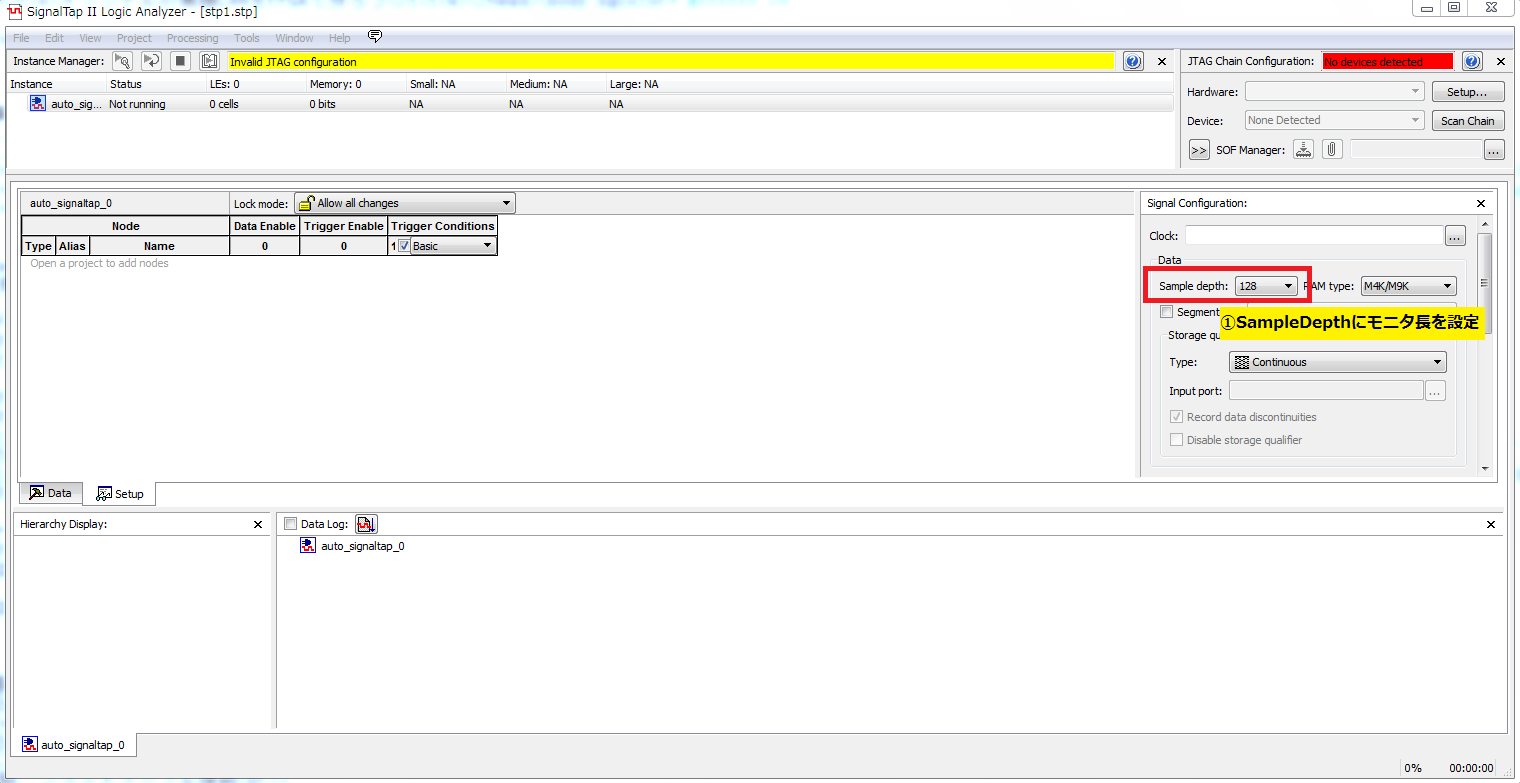

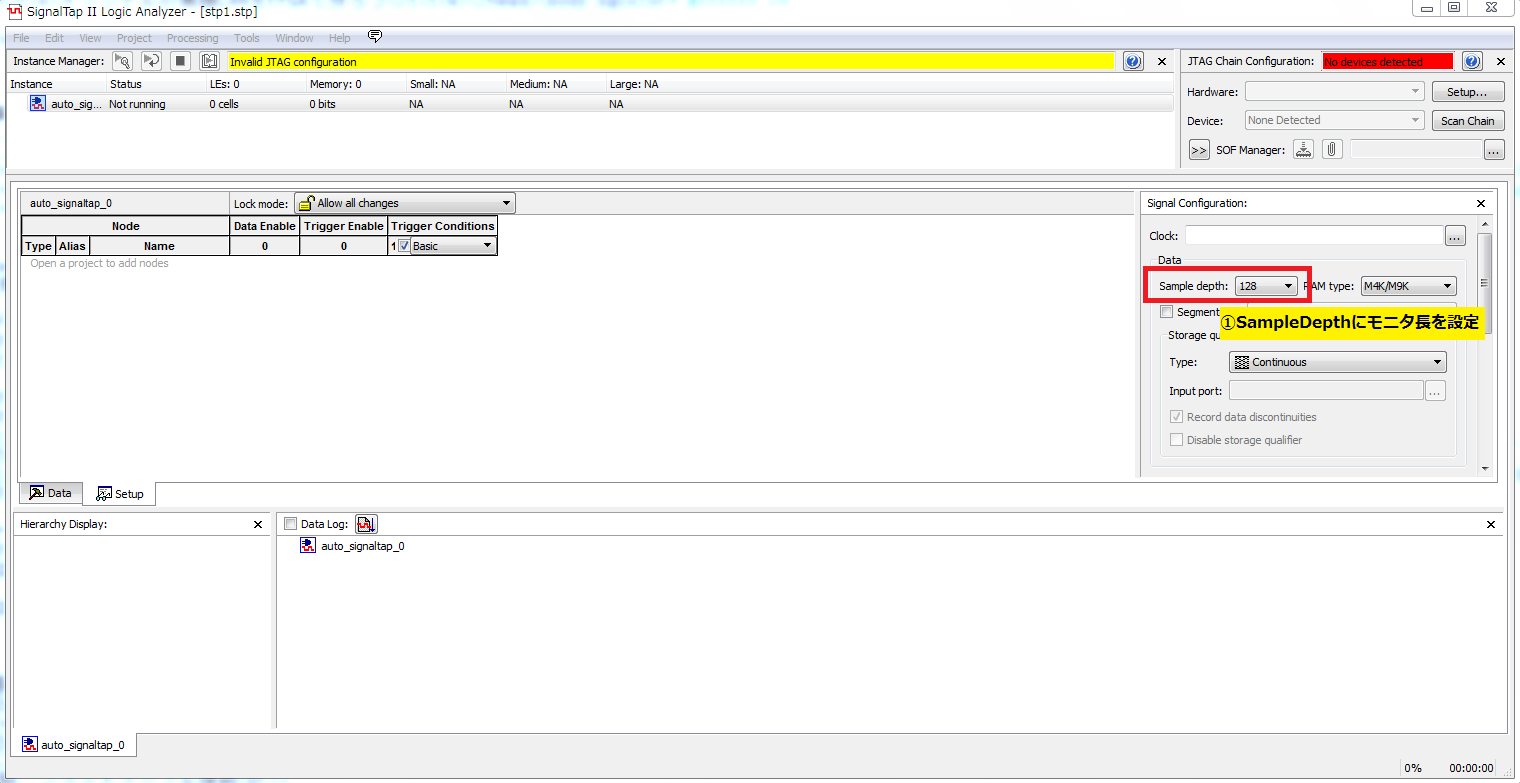

儌僯僞挿偼丄sample depth偱愝掕偟傑偡丅偁傑傝挿偔偡傞偲SRAM嬻偒偑懌傝側偔側傝傑偡偺偱拲堄偱偡丅崱夞偼丄128偵愝掕偟傑偡丅

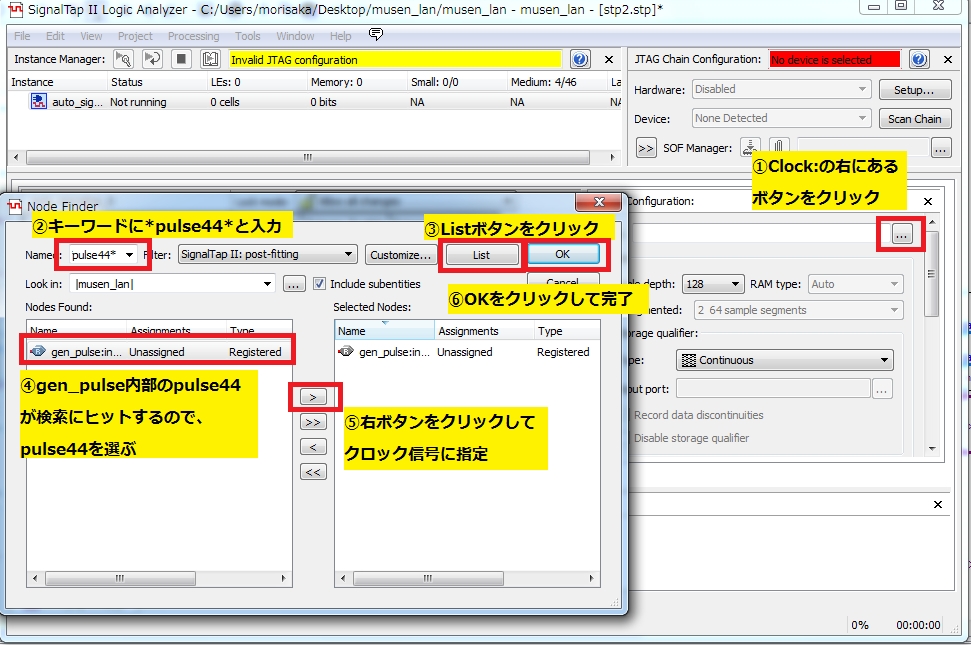

師偵僋儘僢僋傪愝掕偟傑偡丅僋儘僢僋偵愝掕偟偨怣崋偺侾僷儖僗枅偵侾夞怣崋傪SRAM偵庢傝崬傒傑偡丅

掅懍ADC偑48Ksps偱摦偒傑偡偺偱丄摨偠48kHz廃婜偺怣崋傪僋儘僢僋偵愝掕偟傑偡丅

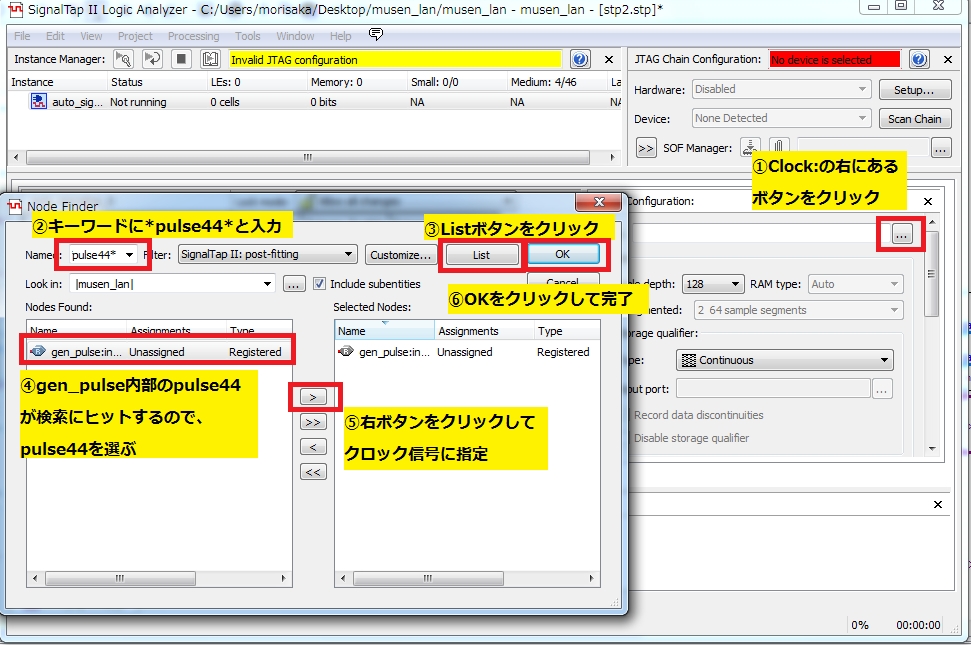

丂嘆Clock:偺塃偺傎偆偵偁傞儃僞儞傪僋儕僢僋

丂嘇僉乕儚乕僪偵*pulse44*偲擖椡偟傑偡

丂嘊List儃僞儞傪僋儕僢僋偟偰丄FPGA撪偺怣崋偐傜*pulse44*傪専嶕偟傑偡

丂丂仸僐儞僷僀儖嵪傒偺FPGA僼傽乕儉僂僃傾偵懳偟偰偺専嶕婡擻偱偡丅

丂丂丂栚揑偺怣崋傪専嶕偝偣傞偨傔偵僔僌僫儖僞僢僾傪巊偆慜偵堦扷僐儞僷僀儖偟偰偍偔昁梫偑偁傝傑偡丅

丂嘋gen_pulse撪晹偵偁傞pulse44偑専嶕偝傟傑偡偺偱丄偙偺怣崋傪慖傃傑偡

丂嘍塃儃僞儞傪僋儕僢僋偟偰丄gen_pulse撪晹偵偁傞pulse44傪僋儘僢僋偲偟偰愝掕偟傑偡

丂嘐OK傪僋儕僢僋偟偰姰椆偱偡

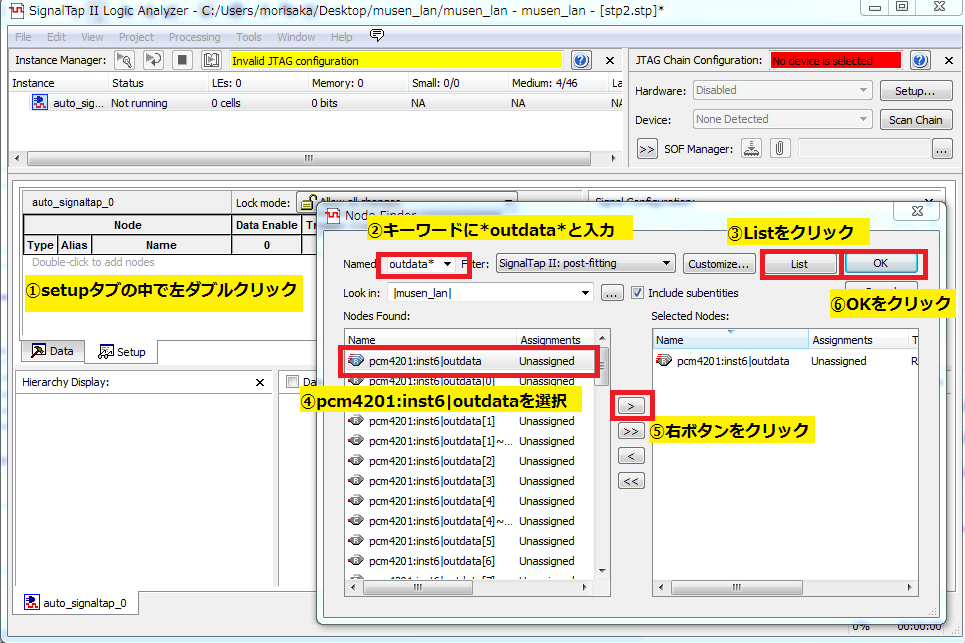

師偵儌僯僞偡傞怣崋傪愝掕偟傑偡丅

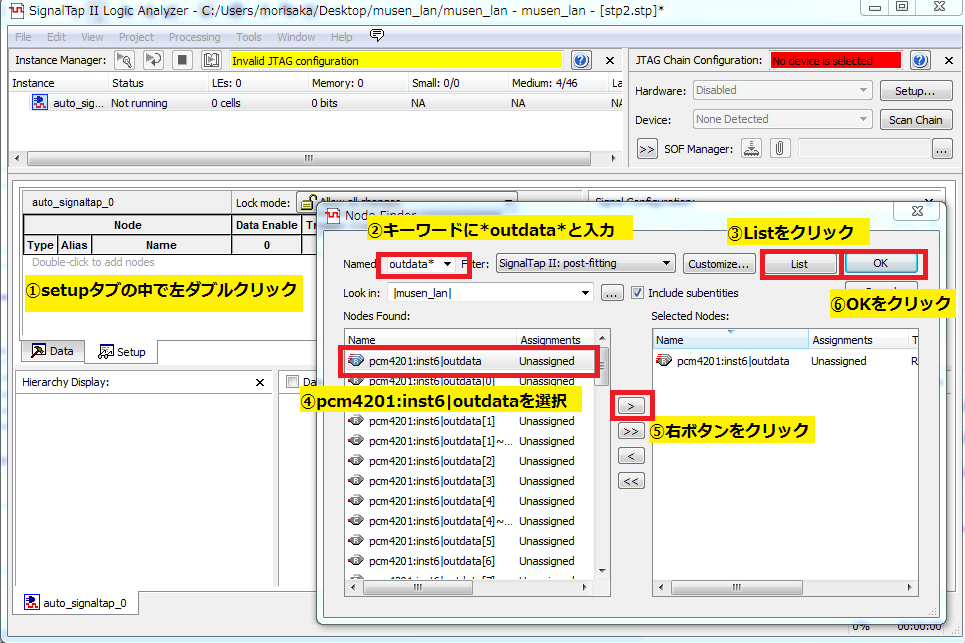

丂嘆setup僞僽偺拞偱嵍僟僽儖僋儕僢僋偟傑偡

丂嘇僉乕儚乕僪偵*outdata*偲擖椡偟傑偡

丂嘊List儃僞儞傪僋儕僢僋偟偰丄FPGA撪偺怣崋偐傜*outdata*傪専嶕偟傑偡

丂丂仸僐儞僷僀儖嵪傒偺FPGA僼傽乕儉僂僃傾偵懳偟偰偺専嶕婡擻偱偡丅

丂丂丂栚揑偺怣崋傪専嶕偝偣傞偨傔偵僔僌僫儖僞僢僾傪巊偆慜偵堦扷僐儞僷僀儖偟偰偍偔昁梫偑偁傝傑偡丅

丂嘋pcm4201儌僕儏乕儖偺拞偺outdata偑専嶕偝傟傑偡偺偱丄偙偺怣崋傪慖傃傑偡

丂嘍塃儃僞儞傪僋儕僢僋偟偰丄pcm4201儌僕儏乕儖偺拞偺outdata傪儌僯僞怣崋偲偟偰愝掕偟傑偡

丂嘐OK傪僋儕僢僋偟偰姰椆偱偡

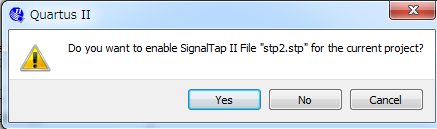

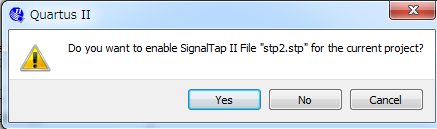

儌僯僞挿丄僋儘僢僋丄儌僯僞怣崋偺愝掕偑廔傢偭偨傜曐懚偟傑偡丅僔僌僫儖僞僢僾偺儊僀儞儊僯儏乕丂仺丂File丂仺丂Save丂偱曐懚偱偒傑偡丅

曐懚偟偨屻偱僟僀傾儘僌偑弌偰偒傑偡丅偙偺僟僀傾儘僌偱Yes傪僋儕僢僋偟偰丄師偵僐儞僷僀儖偡傞帪偼丄儌僯僞偺偨傔偺SRAM傗JTAG偱撉傒弌偡偨傔偺婡擻偑FPGA僼傽乕儉偵嶌傝偙傑傟傑偡丅

忋偱愢柧偟偨僟僀傾儘僌偱娫堘偊偰僋儕僢僋偟偰傕丄奐敪娐嫬偺儊僀儞夋柺偐傜愝掕傪捈偡偙偲偑偱偒傑偡丅

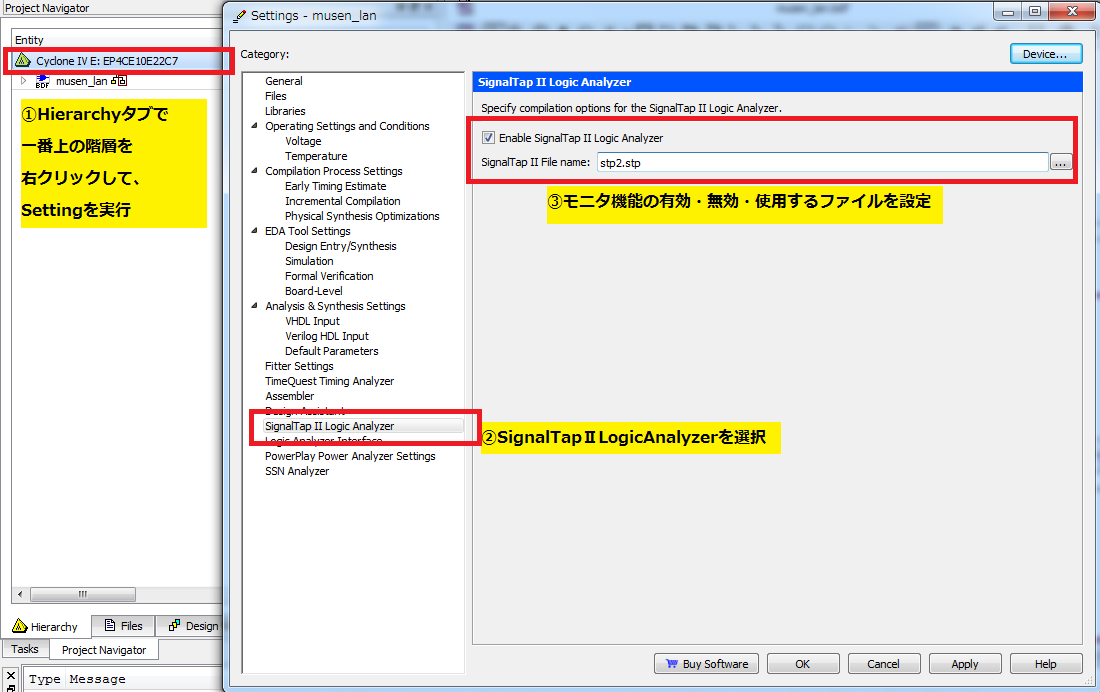

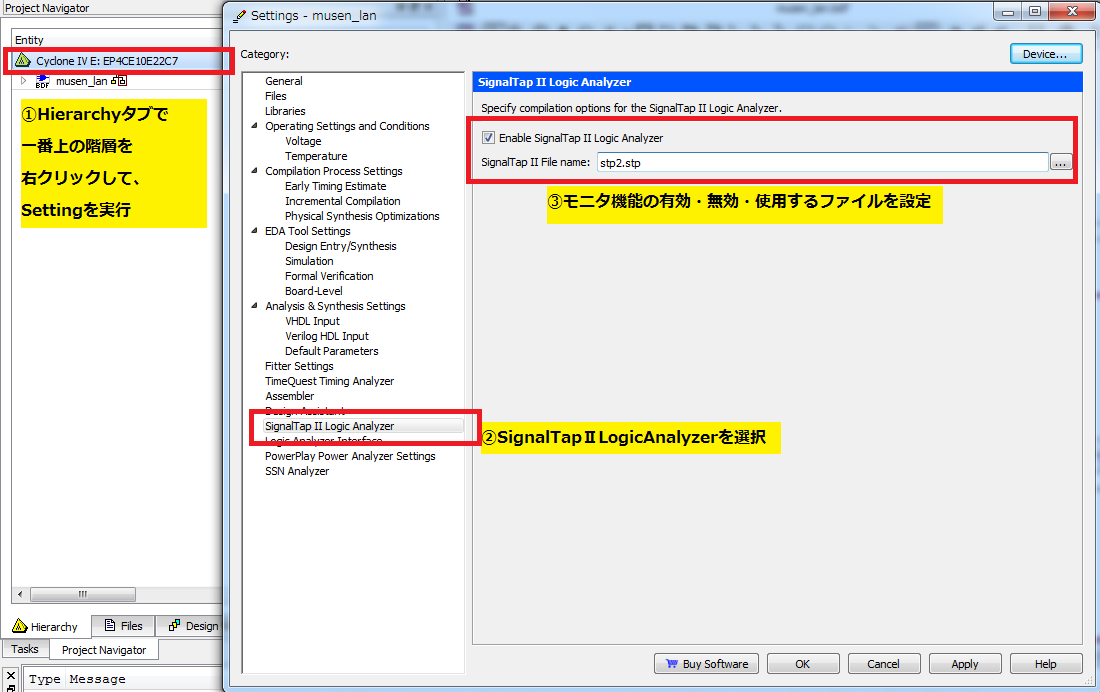

丂嘆Hierarchy僞僽偺堦斣忋偺奒憌偱塃僋儕僢僋偟偰settings傪幚峴偟傑偡

丂嘇SignalTap嘦Analyzer傪慖戰

丂嘊儌僯僞偡傞婡擻偺桳岠丒柍岠丒巊梡偡傞僼傽僀儖傪慖戰

僔僌僫儖僞僢僾偺愝掕偑廔傢偭偨傜丄嵞搙僐儞僷僀儖傪偐偗偰FPGA撪晹偵儌僯僞梡偺SRAM偺嶌傝崬傒側偳傪峴偄傑偡丅

怣崋偺儌僯僞傪巒傔傞慜偵丄FPGA彂偒崬傒婍傪FPGA儃乕僪偺JTAG僺儞偵愙懕偟偰偍偒傑偡丅愙懕曽朄偼16儁乕僕栚傪偛棗壓偝偄丅

FPGA儃乕僪偺僆乕僨傿僆擖椡偲偟偰1KHz偺惓尫攇傪愙懕偟傑偟偨丅惓忢偵掅懍ADC偑摦嶌偡傞偲僔僌僫儖僞僢僾偱惓尫攇偑儌僯僞偱偒傞偼偢偱偡丅

僐儞僷僀儖偑廔傢偭偨傜丄儊僀儞儊僯儏乕丂仺丂Tools丂仺丂SignalTap嘦LogicAnalizer偵偰僔僌僫儖僞僢僾傪棫偪忋偘傑偡丅

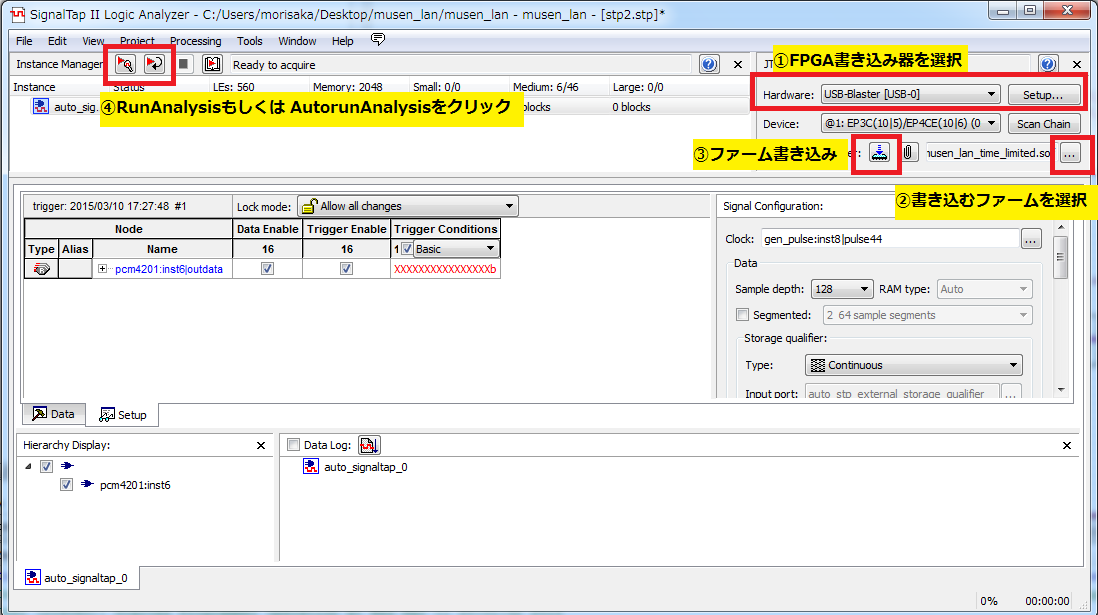

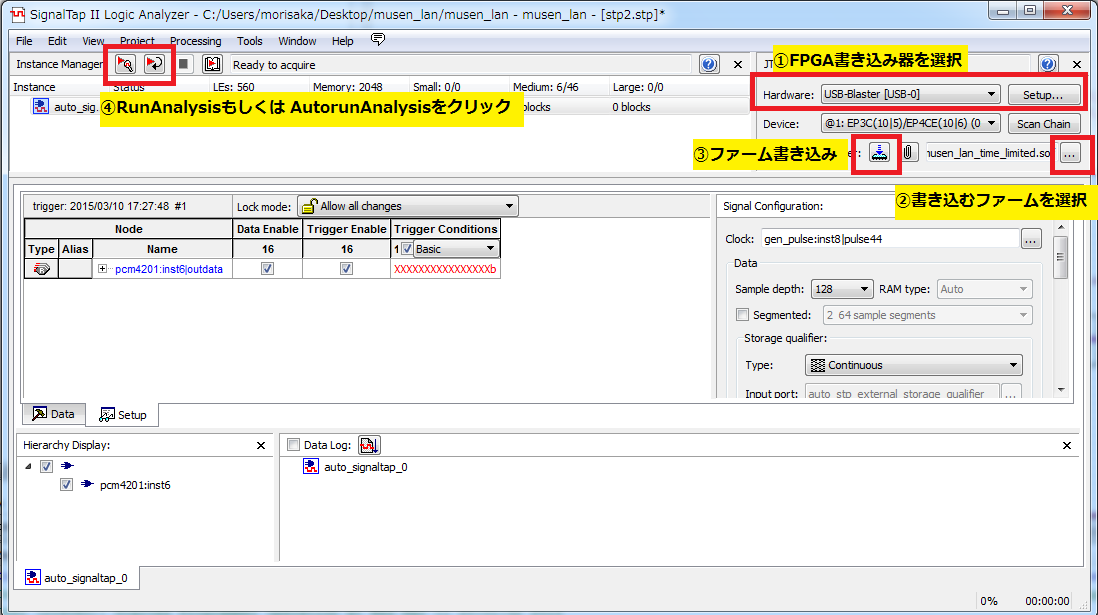

丂嘆彂偒崬傒婍傪慖戰偟傑偡丅暋悢偺彂偒崬傒婍傪PC偵愙懕偟偰偄傞応崌偼巊梡偡傞傎偆偺彂偒崬傒婍傪慖戰偟偰偔偩偝偄丅

丂嘇彂偒崬傓僼傽乕儉乮奼挘巕 .sof乯傪慖戰偟傑偡丅愭傎偳僐儞僷僀儖偟偨僼傽乕儉傪慖戰偟偰偔偩偝偄丅

丂嘊僼傽乕儉傪彂偒崬傒傑偡丅僼傽乕儉彂偒崬傒偑姰椆偟偨傜NCO偵偮偄偰偺惂尷帠崁偺僟僀傾儘僌偑弌傑偡偐傜丄

丂丂OK傪僋儕僢僋偟偰僟僀傾儘僌傪暵偠偰偔偩偝偄丅

丂嘋Run Analysis丂傕偟偔偼丄Autorun Analysis傪僋儕僢僋偟偰掅懍ADC偺16價僢僩偺怣崋傪PC偵庢傝崬傒傑偡丅

仸Run Analysis丂偲丄Autorun Analysis偺堘偄偵偮偄偰丄

丒Run Analysis丂傪僋儕僢僋偡傞偲丄僋儕僢僋偑僩儕僈偲側傝128偺儌僯僞挿偺SRAM僨乕僞庢傝崬傒丂仺 PC偵揮憲傪峴偄傑偡

丒Autorun Analysis丂傪僋儕僢僋偡傞偲丄SRAM僨乕僞庢傝崬傒丂仺 PC偵揮憲丂仺 SRAM僨乕僞庢傝崬傒丂仺 PC偵揮憲...傪孞傝曉偟傑偡

Run Analysis丂傕丄Autorun Analysis傕丄尒偨偄弖娫偩偗傪儌僯僞偡傞偙偲偑擄偟偄偱偡丅尒偨偄弖娫傪儌僯僞偡傞偨傔偵丄乽FPGA撪晹偺怣崋偑xxx偵側偭偨偺傪僩儕僈偵SRAM僨乕僞庢傝崬傓乿

偲偄偆巊偄曽傕傕偱偒傑偡丅偙傟偼丄暿偺婡夛偵愢柧偟傑偡丅

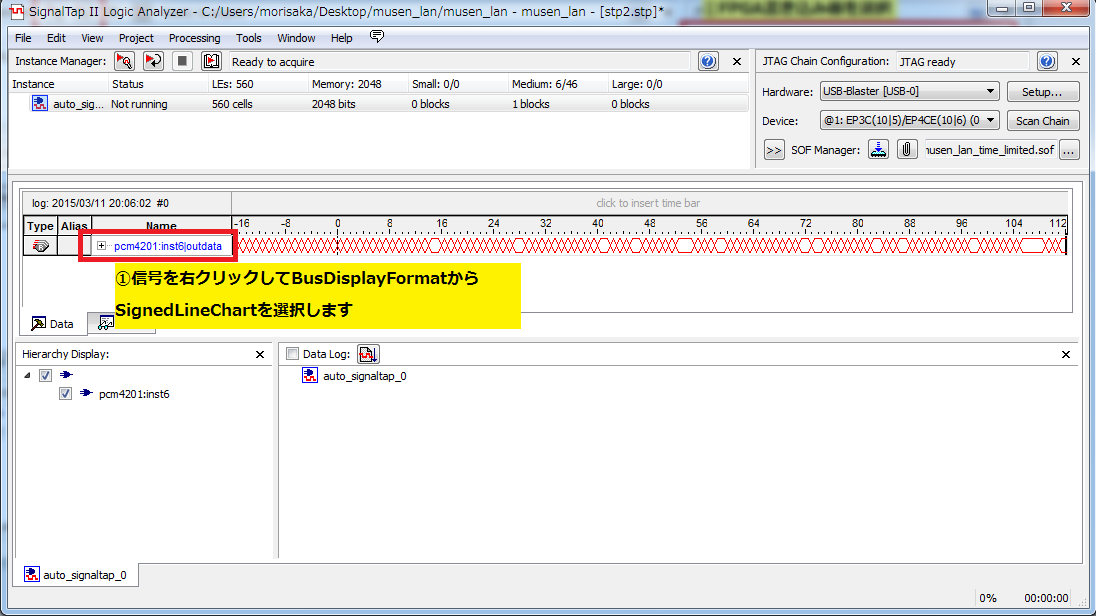

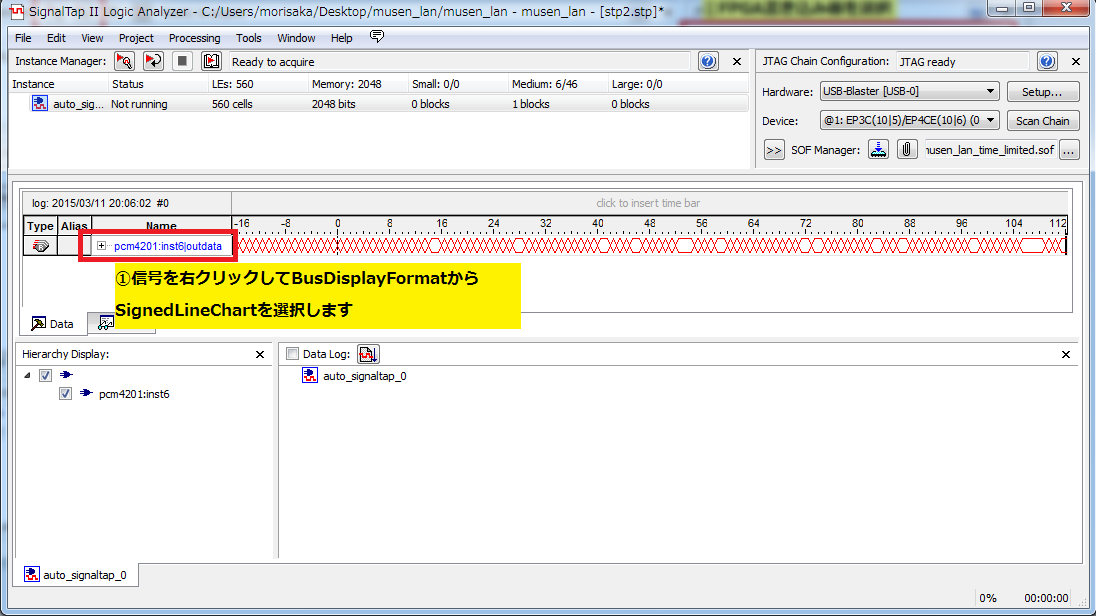

Run Analysis丂傕偟偔偼丄Autorun Analysis傪僋儕僢僋偡傞偲丄掅懍ADC偱庢傝崬傫偩僨乕僞偑尒傟傑偡丅僨僼僅儖僩偱偼16恑悢昞帵偱傛偔傢偐傝傑偣傫偺偱丄

丂嘆怣崋柤傪塃僋儕僢僋偟偰BusDisplayFormat偐傜SignedLineChart傪慖戰偟傑偡丅

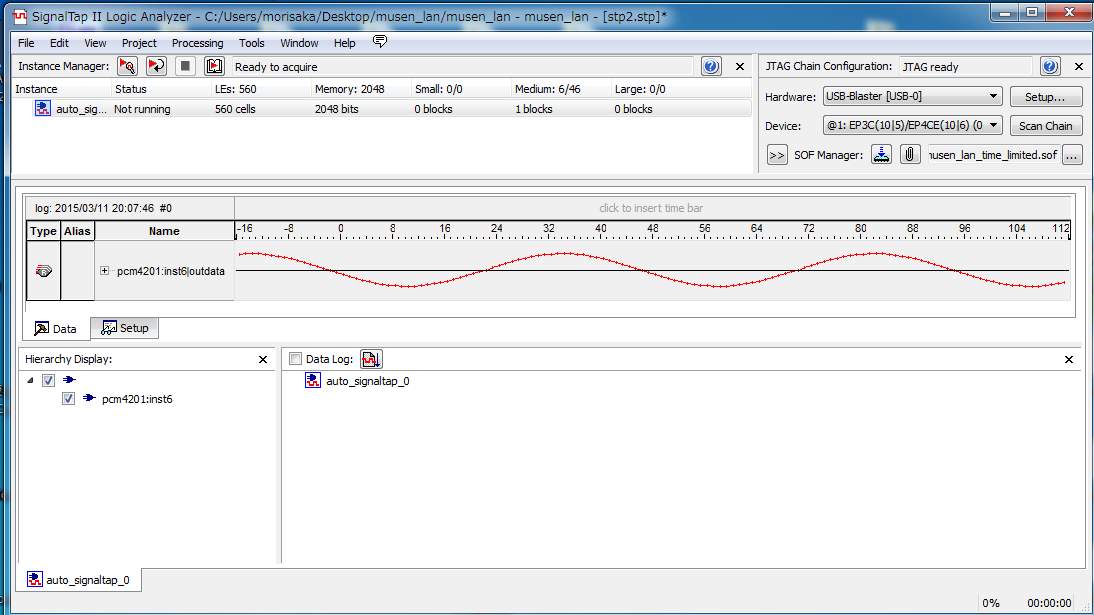

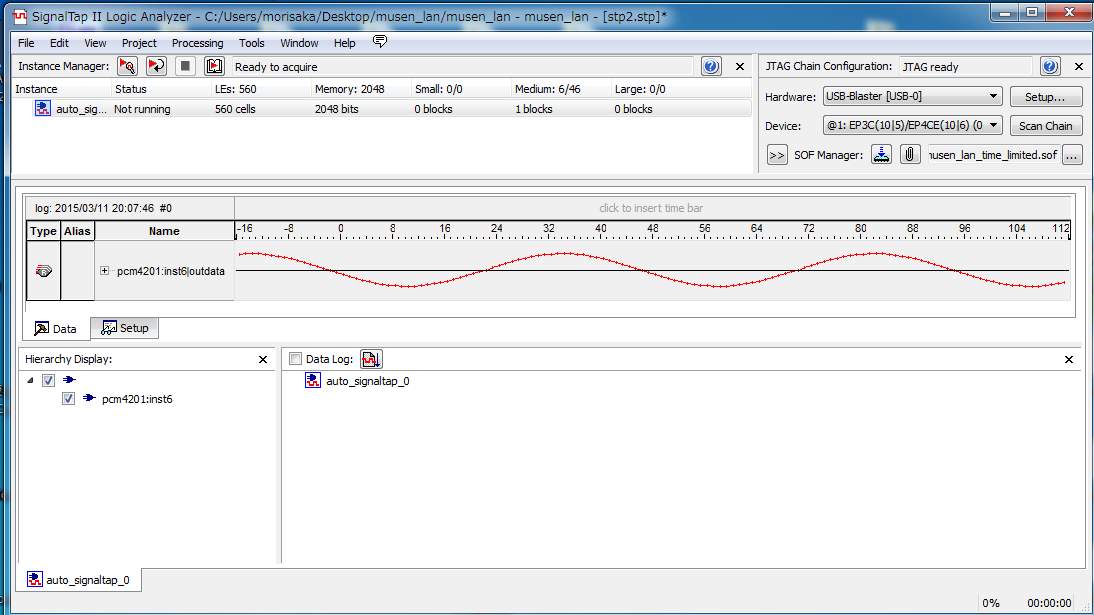

16價僢僩偺僨乕僞偑僌儔僼偱昞帵偝傟傑偡丅惓尫攇偑掅懍ADC偱庢傝崬傑傟偰偄傞偙偲偑妋擣偱偒傑偟偨丅掅懍ADC傑傢傝偼惓忢偵摦偄偰偄傞偲偄偊偦偆偱偡丅

師夞傕丄憲怣懁FPGA偺幚婡僨僶僢僌傪恑傔偰偄偒傑偡丅

2015擭3寧11擔 婰

18儁乕僕栚偵懕偔

栠傞