オリジナルの無線LANをFPGAで作ろう 13ページ目

過去の記事はこちら

1ページ目 2ページ目 3ページ目

4ページ目 5ページ目

6ページ目 7ページ目 8ページ目 9ページ目 10ページ目

11ページ目 12ページ目

1-受信側FPGA-8ビットデータからオーディオデータへの変換

引き続き受信側FPGAのファームを作っていきます。

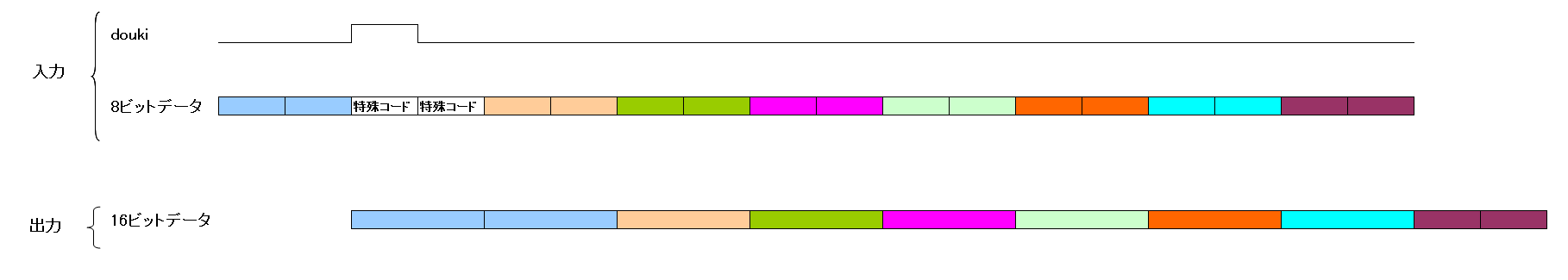

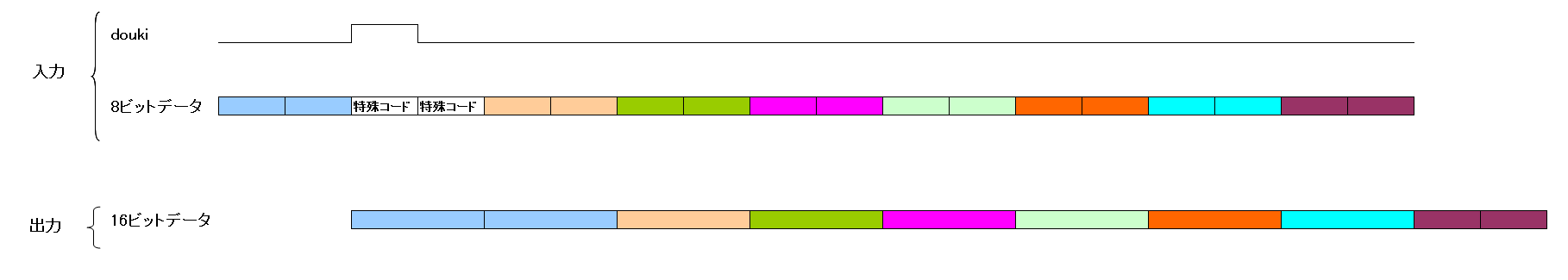

前のページで作ったモジュールからは8ビット96KSpsのデータが得られます。8ビットのデータ2個を1つにまとめて、16ビット48Kspsのデータに変換します。

16ビット48Kspsのデータをオーディオデータとして、低速DACに入れると送信した音声信号が復元されます。

変換モジュールの名前をcode_2_audioにします。code_2_audioモジュールの働きはもうひとつあって、特殊コードを直前のデータに置き換える働きを持ちます。

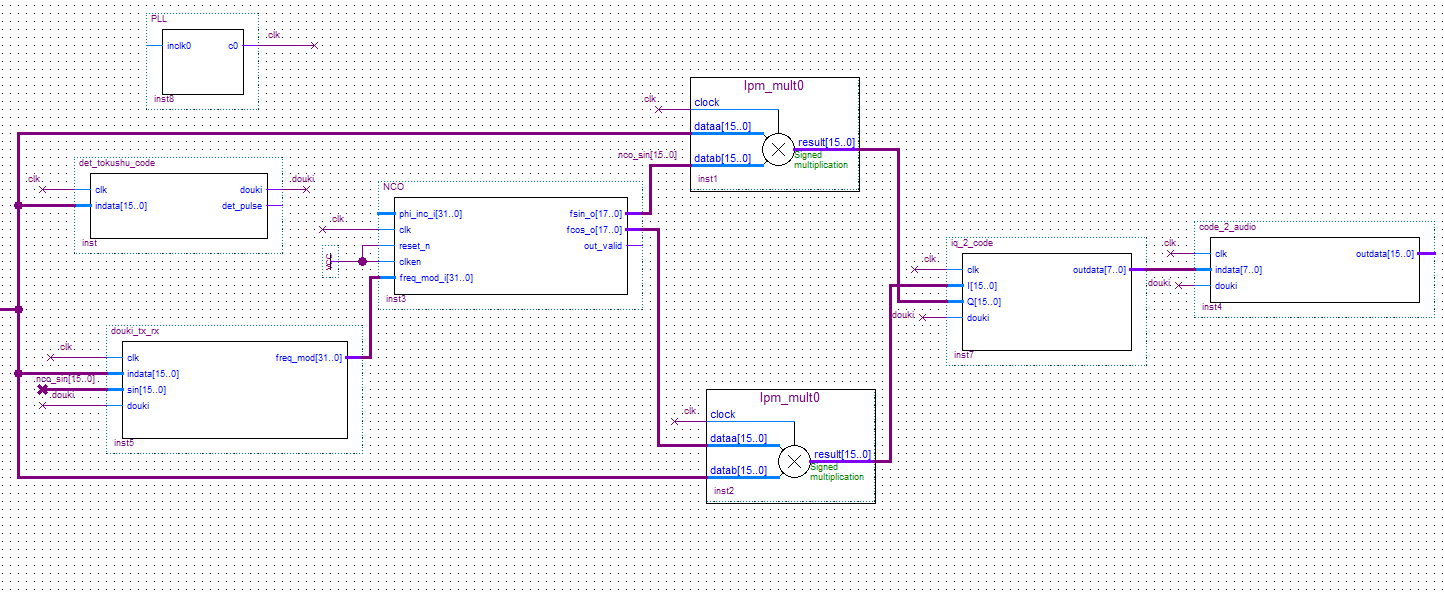

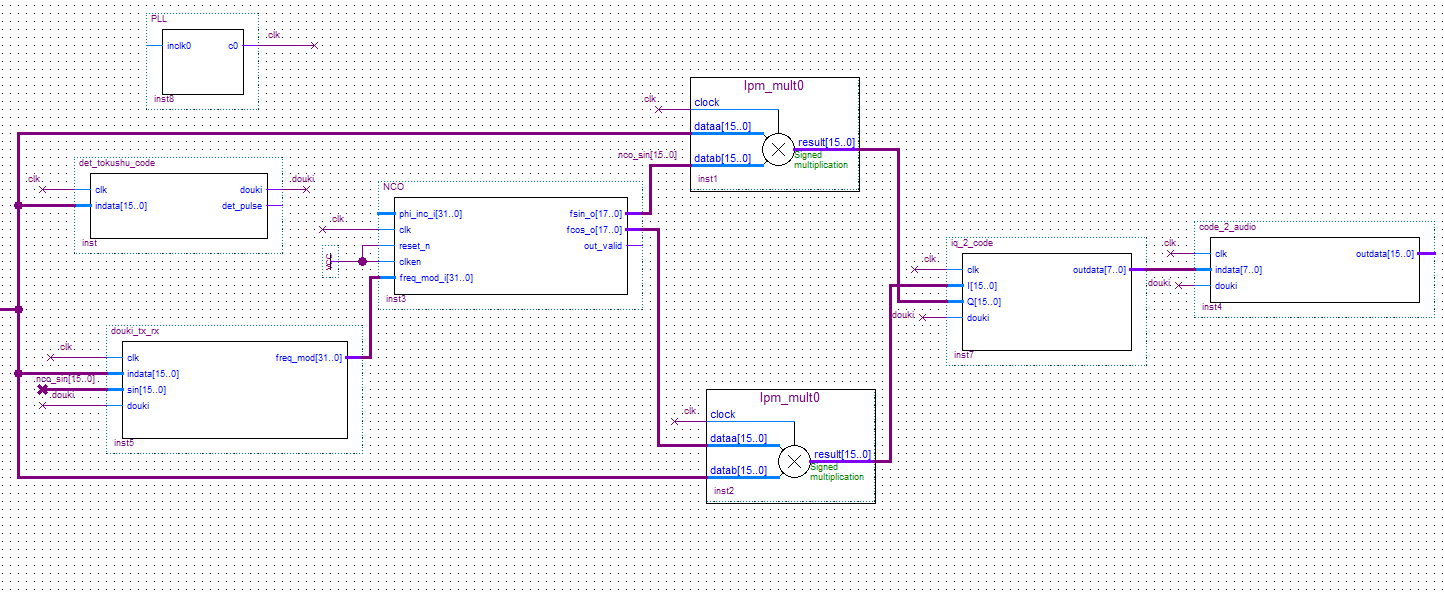

code_2_audioモジュールはVerilogで作成しました。ソースコードはこちらからダウンロードしてください。code_2_audioモジュールはシンボル化して回路図に配置してください。

前のページで作成済みのiq_2_codeも一緒に配置して結線の終わった状態です。

PLLの追加もついでに行いました。送信側と同じように24.676MHzの水晶を3逓倍して73.728MHzを生成するPLLを入れ込んでいます。

PLL生成方法は6ページ目をご覧下さい。

次回は引き続き受信側のFPGAファームを作っていきます。

2015年2月14日 記

14ページ目に続く

戻る